## AŇO 2020 3300 - 001706 / 19 - 001

**Creado:** 16-09-2020

**Iniciador:** MESA DE ENTRADAS - INFORMATICA

COSTI ULISES

**Extracto:** E/TRABAJO FINAL DE TESINA DE GRADO

DE LA CARRERA LICENCIATURA EN

INFORMATICA TITULADA "ACELERACION DEL ALGORITMO FLOYD-WARSHALL SOBRE INTEL XEON PHI KNL", BAJO LA DIRECCION DEL DR. ENZO RUCCI Y EL

ESP. FRANCO CHICHIZOLA.---

La Plata, 16 de Septiembre de 2020

Sra. Decana Facultad de Informática - UNLP Lic. Patricia Pesado S D

De mi mayor consideración:

Tengo el agrado de dirigirme a Ud. con el objeto de presentar el informe final de mi tesina de grado "Aceleración del Algoritmo Floyd-Warshall sobre Intel Xeon Phi KNL" de la carrera Licenciatura en Informática.

Sin otro particular saludo a ud. muy atte.

APU Ulises Costi

Dr Enzo Rucci

Director

Esp Franco Chichizola

Director

## **FACULTAD DE INFORMÁTICA**

## TESINA DE LICENCIATURA

TÍTULO: Aceleración del Algoritmo Floyd-Warshall sobre Intel Xeon Phi KNL

**AUTORES:** Ulises Costi

**DIRECTOR:** Enzo Rucci, Franco Chichizola

CODIRECTOR:

ASESOR PROFESIONAL:

CARRERA: Licenciatura en Informática

#### Resumen

En la última década, los aceleradores han tomado mayor protagonismo en la comunidad de HPC. Recientemente, Intel introdujo la segunda generación de aceleradores Xeon Phi, con nombre en código Knights Landing (KNL), el cual trae importantes mejoras con respecto a su predecesor. Esta tesina se enfoca en evaluar el uso de la arquitectura KNL para acelerar el algoritmo Floyd-Warshall (FW). Partiendo de una versión paralela "clásica" del mismo, se muestra cómo aumenta el rendimiento con cada optimización aplicada hasta llegar a la solución óptimizada, con la cual se logró un pico de 1039 GFLOPS.

#### Palabras Clave

Xeon Phi, Knighs Landing, Floyd-Warshal, AVX-512, MCDRAM, HPC, Hyper-Threading, grafo, caminos mínimos.

# Trabajos Realizados

Se presentó la arquitectura Xeon Phi KNL, se enunció el problema del camino mínimo en grafos, y al algoritmo FW como una de sus soluciones. Con el fin de lograr una versión de FW optimizada para KNL, se llevó a cabo un desarrollo incremental iterativo; partiendo del algoritmo base, se aplicaron diferentes técnicas de optimización comparando los resultados de rendimiento en cada caso. En una segunda etapa, se desarrollaron versiones variantes del programa, a modo de evaluar diferentes alternativas y parámetros.

#### Conclusiones

El objetivo planteado en esta tesina se considera satisfecho al lograr una versión de FW optimizada para Xeon Phi KNL, acompañada del análisis e investigación que fueron necesarios para su desarrollo. Se investigó acerca de la arquitectura, el algoritmo, y sobre las diferentes técnicas de optimización. También fueron desarrolladas versiones variantes del programa, con el fin de evaluar su utilidad en distintos escenarios alternativos. Para beneficio de la comunidad, el código se encuentra disponible en un repositorio público.

#### Trabajos Futuros

Por un lado, se planea continuar refinando la optimización del programa desarrollado en este trabajo, ya que es probable que se le pueda extraer aún más rendimiento al KNL con este algoritmo. Por otro lado, siendo las GPU los aceleradores dominantes en la actualidad, resulta interesante utilizar FW para comparar el rendimiento entre ambas arquitecturas.

Fecha de la presentación: Sep 2020

# Aceleración del Algoritmo Floyd-Warshall sobre Intel Xeon Phi KNL

Ulises Costi Facultad de Informática Universidad Nacional de La Plata

Director: Dr. Enzo Rucci

Director: Esp. Franco Chichizola

Tesina presentada para obtener el grado de Licenciado en Informática Septiembre 2020

## Resumen

Desde hace años, los aceleradores van tomando mayor protagonismo en la comunidad de HPC. Con la introducción de los Xeon Phi de segunda generación, con nombre en código Knighs Landing (KNL), la comunidad dispone de un nuevo acelerador x86 que trae importantes mejoras con respecto a su predecesor. Entre ellas se destacan la ejecución fuera de orden, la duplicación de la cantidad de VPUs, y la integración de una memoria de alto ancho de banda.

Una de las áreas bien conocidas por demandar gran poder de cómputo es la teoría de grafos, siendo el algoritmo Floyd-Warshall (FW) un caso bien conocido de la misma. La popularidad y alta demanda computacional de FW lo vuelve un caso interesante de análisis en HPC. Es por este motivo que esta tesina se enfoca en evaluar el uso de arquitectura Xeon Phi KNL para acelerar el algoritmo FW. Partiendo de una versión paralela "clásica" de FW, se muestra cómo aumenta el rendimiento con cada optimización aplicada hasta llegar a la solución optimizada, con la cual se logró un pico de 1039 GFLOPS. Complementariamente, se analizaron diferentes variantes de la implementación, con el fin de evaluar su utilidad en distintos escenarios alternativos. Por último, el código se encuentra disponible para beneficio de la comunidad académica, científica y productiva.

# **Agradecimientos**

A mi madre, por el esfuerzo y acompañamiento durante todos estos años.

A mis abuelos y mi novia, por la colaboración y el apoyo incondicional.

A Víctor, Guillermo, Gustavo y Carlos, por ser mi inspiración para elegir esta carrera.

A Enzo y Franco, por su labor excepcional como directores de esta tesina.

A la Facultad de Informática y el LIDI, por brindarme los medios y recursos para realizar este trabajo.

# Índice general

| Capítulo 1 Introducción                                                     | 1          |

|-----------------------------------------------------------------------------|------------|

| 1.1. Motivación                                                             | 1          |

| 1.2. Objetivos y metodología                                                |            |

| 1.3. Contribuciones                                                         |            |

| 1.4. Publicaciones                                                          | 3          |

| 1.5. Organización                                                           | 3          |

| Capítulo 2 Intel Xeon Phi Knighs Landing                                    | 4          |

| 2.1. Organización y arquitectura                                            | 4          |

| 2.1.1. Orígen                                                               |            |

| 2.1.2. Novedades de KNL con respecto a las versiones anteriores de Xeon Phi |            |

| 2.1.3. Unidad de replicación escalable de la arquitectura                   |            |

| 2.1.4. Modos de ejecución (modos cluster)                                   |            |

| 2.1.5. Tipos de memoria (MCDRAM y DDR)                                      |            |

| 2.1.6. Modos de memoria                                                     |            |

| 2.1.7. Simultaneous Multi Threading (SMT)                                   |            |

| 2.2. Modelos de programación                                                |            |

| 2.2.1. OpenMP                                                               |            |

| 2.3. Optimizaciones                                                         |            |

| 2.3.1. Modos Cluster                                                        |            |

| 2.3.2. Modos de memoria                                                     |            |

| 2.3.3. Elección de cantidad de hilos por núcleo (SMT)                       |            |

| 2.3.4. Afinidad de hilos con núcleos                                        |            |

| 2.3.5. MCDRAM y DDR                                                         |            |

| 2.3.6. Procesamiento vectorial (SIMD)                                       |            |

| 2.3.7. Alineamiento de datos en memoria                                     |            |

| 2.3.8. Desenrollado de bucles                                               |            |

| 2.4. Resumen.                                                               |            |

|                                                                             |            |

| Capítulo 3 Algoritmos para caminos mínimos en grafos                        | .29        |

| 3.1. Problema de caminos mínimos en grafos                                  | 29         |

| 3.2. Algoritmos para caminos mínimos en grafos                              |            |

| 3.2.1. Algoritmo Floyd-Warshall                                             |            |

| 3.3. Estado del arte sobre aceleración del algoritmo Floyd-Warshall         | 32         |

| 3.4. Resumen                                                                | 33         |

| Capítulo 4 Aceleración del algoritmo Floyd-Warshall sobre Xeon Phi          |            |

| KNL                                                                         | .34        |

|                                                                             |            |

| 4.1. Plataforma de pruebas                                                  |            |

| 4.2. Configuraciones de las pruebas                                         |            |

| 4.3. Primeras versiones de FW implementadas                                 | 3/<br>37   |

| 45 E VERSION IVALUE-SPEC EVV SECHENCIAL CLASICO                             | <b>1</b> / |

| 4.3.2. Versión <i>Naive-Par</i> : FW "clásico" paralelizado                             | 39  |

|-----------------------------------------------------------------------------------------|-----|

| 4.3.3. Versión <i>Block-Sec</i> : Variante de FW con <i>blocking</i>                    | 42  |

| 4.4. Versión <i>Opt-0</i> y sus optimizaciones incrementales                            | 52  |

| 4.4.1. Versión <i>Opt-0</i> : FW con <i>blocking</i> paralelizado                       |     |

| 4.4.2. Versión <i>Opt-1</i> : Optimización utilizando MCDRAM                            | 58  |

| 4.4.3. Versión Opt-2: Optimización utilizando vectorización guiada (SSE)                | 60  |

| 4.4.4. Versión Opt-3: Optimización utilizando vectorización guiada (AVX2)               | 62  |

| 4.4.5. Versión Opt-4: Optimización utilizando vectorización guiada (AVX512)             | 63  |

| 4.4.6. Versión Opt-5: Optimización utilizando alineación de datos en memoria            | 65  |

| 4.4.7. Versión <i>Opt-6</i> : Optimización utilizando predicción de saltos por software |     |

| 4.4.8. Versión <i>Opt-7</i> : Optimización utilizando desenrollado de bucles            |     |

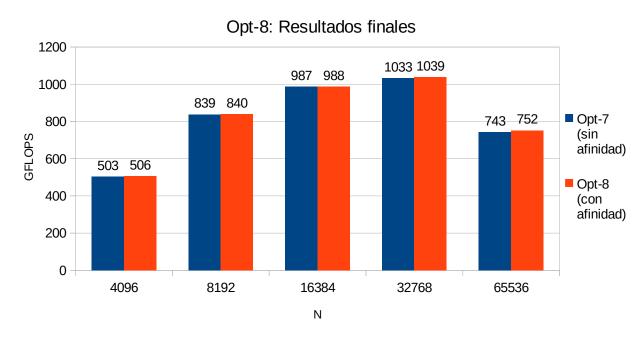

| 4.4.9. Versión <i>Opt-8</i> : Optimización utilizando afinidad de hilos con núcleos     | 75  |

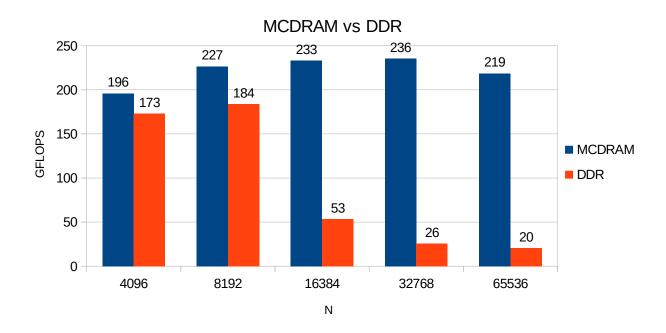

| 4.4.10. Probando eficacia de la MCDRAM sobre el nivel de optimización <i>Opt-5</i>      |     |

| 4.5. Experimentos adicionales                                                           |     |

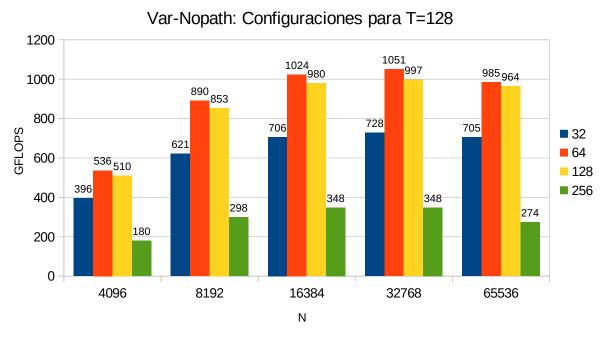

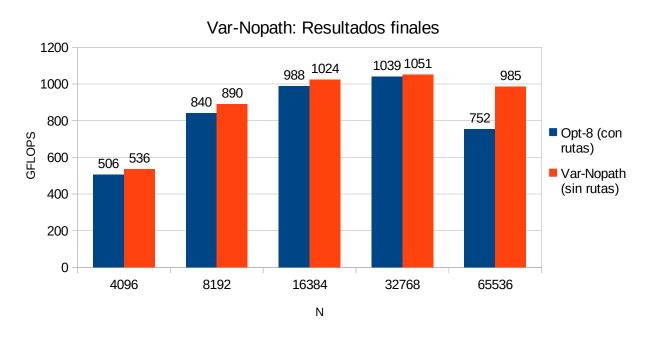

| 4.5.1. Versión Var-Nopath: Variante que omite la matriz de reconstrucción de cami       | nos |

| mínimos                                                                                 |     |

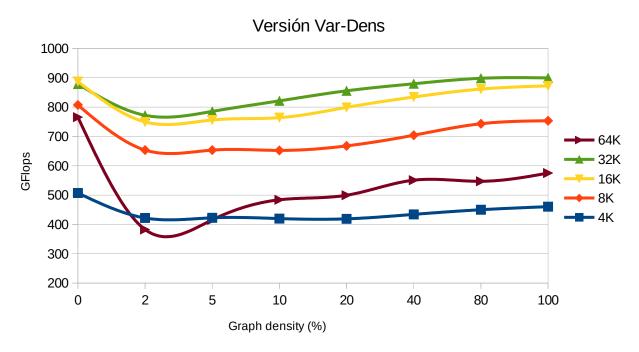

| 4.5.2. Versión Var-Dens: Variando el grado de densidad del grafo de entrada             |     |

| 4.5.3. Versión <i>Var-Prec</i> : Variante con relajación de precisión                   | 81  |

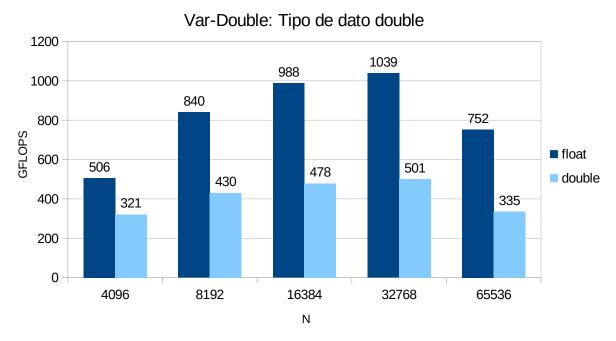

| 4.5.4. Versión <i>Var-Double</i> : Variante con tipo de dato <i>double</i>              |     |

| 4.6. Comparación con trabajos similares                                                 |     |

| 4.7. Resumen                                                                            | 83  |

| Capítulo 5 Conclusiones y trabajos futuros                                              | 86  |

| Capitulo 5 Conclusiones y trabajos futuros                                              | 60  |

| Referencias                                                                             | 80  |

| 1 \C C C C U UJ                                                                         |     |

## Índice de figuras

| Fig 2.1: Diagrama de bloques del paquete del KNL (CPU)                                     | 7  |

|--------------------------------------------------------------------------------------------|----|

| Fig 2.2: Diagrama de bloques de un tile                                                    |    |

| Fig 2.3: Gráfico representativo de los tres modos de memoria del KNL                       |    |

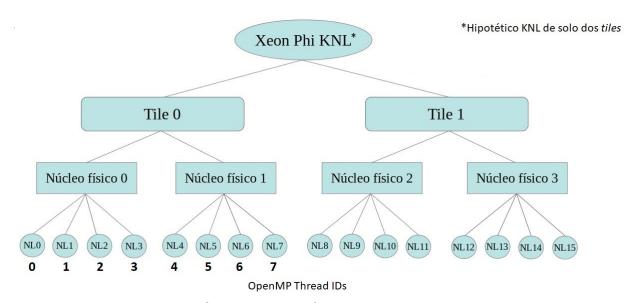

| Fig 2.4: Ejemplo de distribución de hilos con tipo de afinidad "scatter"                   |    |

| Fig 2.5: Ejemplo de distribución de hilos con afinidad "compact"                           |    |

| Fig 2.6: Ejemplo de distribución de hilos con afinidad "balanced"                          |    |

| Fig 2.7: Ejemplo de distribución de hilos con granularidad "core" y tipo de afinidad       |    |

| "balanced"                                                                                 | 19 |

| Fig 2.8: Ejemplo de distribución de hilos con granularidad "tile" y tipo de afinidad       |    |

| "compact"                                                                                  | 19 |

| Fig 2.9: Comparación gráfica del ancho de los registros SIMD del KNL, con la cantidad      | v  |

| tamaño de los datos que caben en ellos                                                     | -  |

| Fig 3.1: Pseudocódigo del algoritmo FW secuencial "clásico"                                |    |

| Fig 4.1: Captura de implementación de FW secuencial "clásico"                              |    |

| Fig 4.2: Captura de pantalla de FW "clásico" con vectores unidimensionales                 |    |

| Fig 4.3: Captura de pantalla de FW "clásico" optimizado ahorrando cómputo redundante       |    |

| (versión Naive-Sec)                                                                        |    |

| Fig 4.4: Captura de pantalla de paralelización simple del FW secuencial "clásico" (versió  |    |

| Naive-Par)                                                                                 |    |

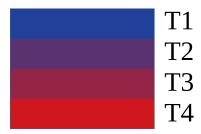

| Fig 4.5: Resultados finales de la versión Naive-Par                                        |    |

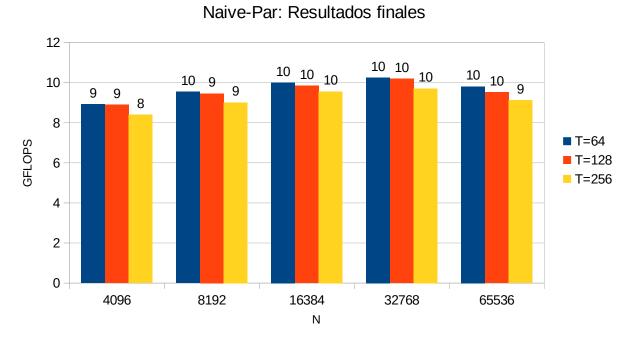

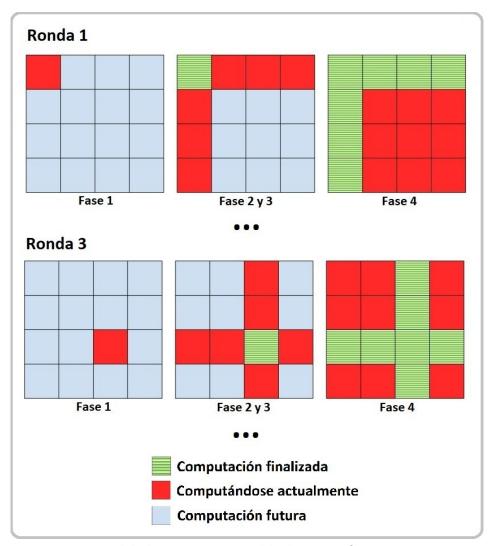

| Fig 4.6: Etapas del algoritmo FW con blocking.                                             |    |

| Fig 4.7: Etapas del algoritmo FW con blocking con fases 2 y 3 en paralelo                  |    |

| Fig 4.8: Pseudocódigo del algoritmo FW con blocking                                        |    |

| Fig 4.9: Captura de pantalla del algoritmo FW con blocking (versión Block-Sec)             |    |

| Fig 4.10: Captura de pantalla de función FW_BLOCK (versión Block-Sec)                      |    |

| Fig 4.11: Captura de pantalla de la función principal de FW paralelo con blocking (version |    |

| Opt-0)                                                                                     |    |

| Fig 4.12: Captura de pantalla de funcion FW_BLOCK_PARALLEL (versión Opt-0)                 | 55 |

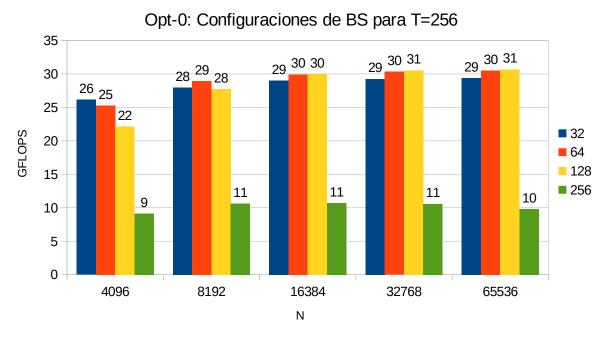

| Fig 4.13: Versión Opt-0. Configuraciones de BS para T=256                                  |    |

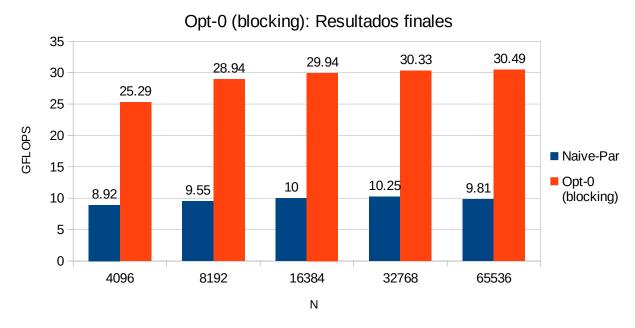

| Fig 4.14: Resultados finales de la versión Opt-0                                           |    |

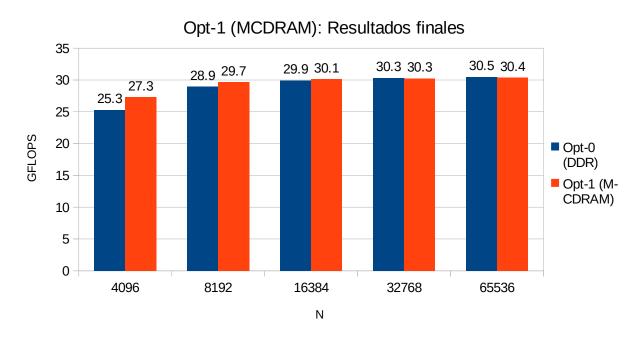

| Fig 4.15: Resultados finales de la versión Opt-1                                           |    |

| Fig 4.16: Captura de pantalla de la función FW_BLOCK (versión Opt-2)                       |    |

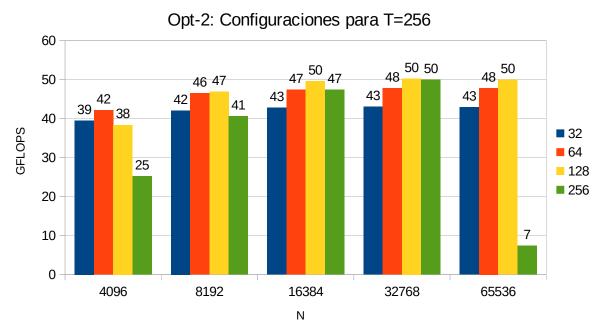

| Fig 4.17: Versión Opt-2. Configuraciones de BS para T=256                                  |    |

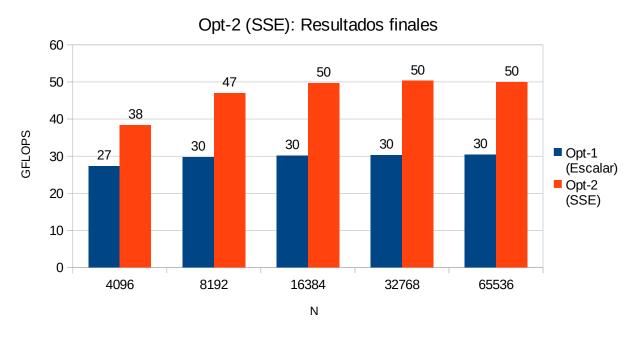

| Fig 4.18: Resultados finales de la versión Opt-2                                           |    |

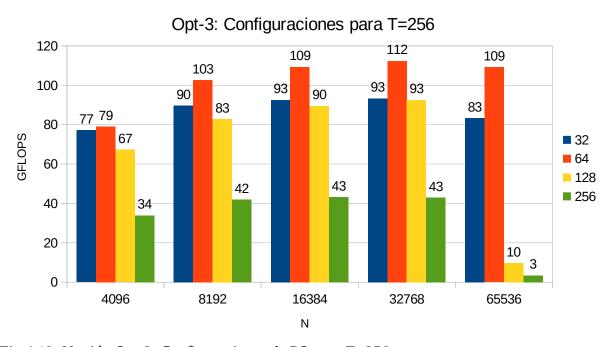

| Fig 4.19: Versión Opt-3. Configuraciones de BS para T=256                                  |    |

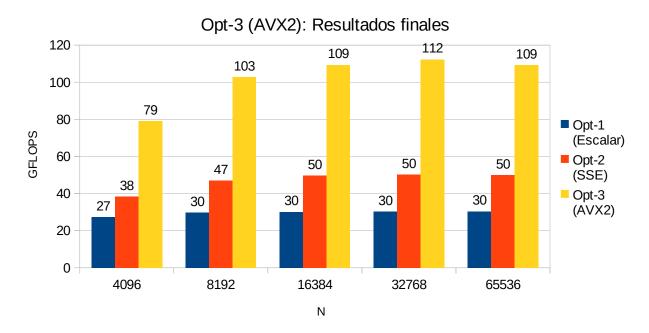

| Fig 4.20: Resultados finales de la versión Opt-3                                           |    |

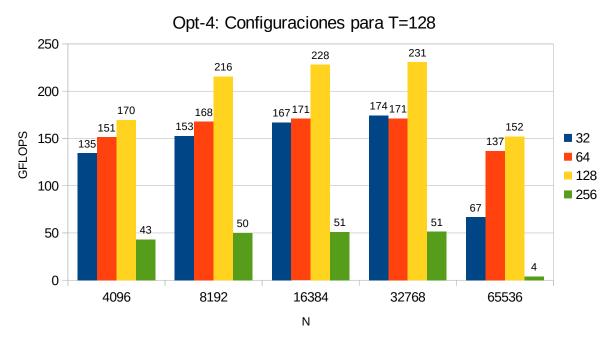

| Fig 4.21: Versión Opt-4. Configuraciones de BS para T=128                                  |    |

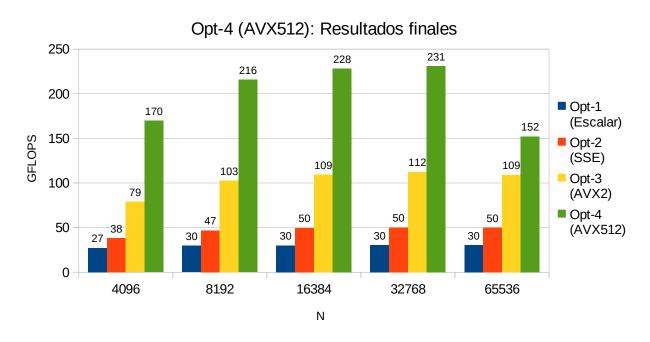

| Fig 4.22: Resultados finales de la versión Opt-4                                           |    |

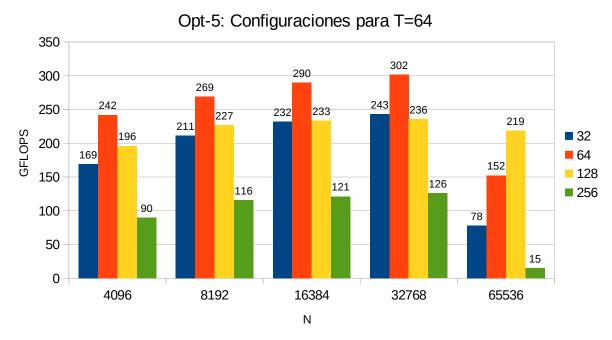

| Fig 4.23: Versión Opt-5. Configuraciones de BS para T=64                                   |    |

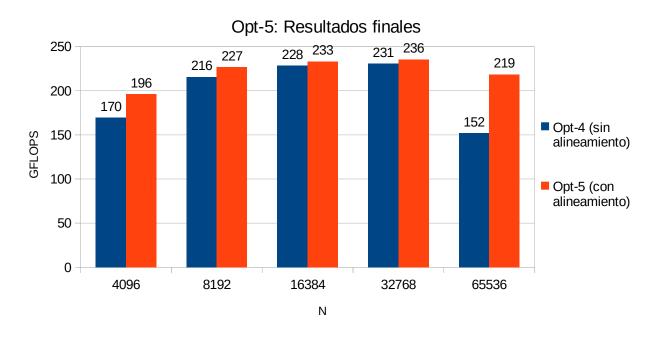

| Fig 4.24: Resultados finales de la versión Opt-5                                           |    |

| Fig 4.25: Captura de pantalla de función FW_BLOCK (versión Opt-6)                          |    |

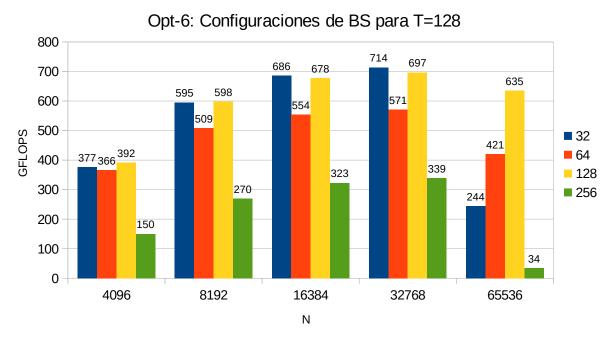

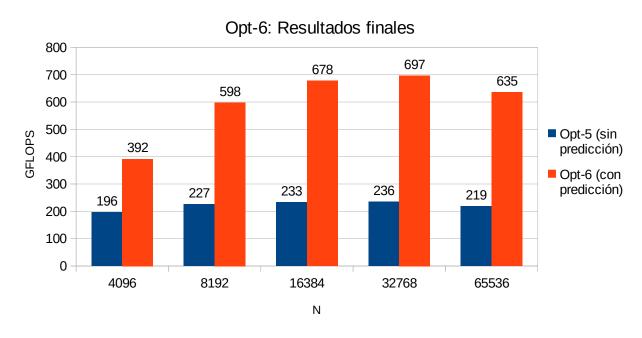

| Fig 4.26: Versión Opt-6. Configuraciones de BS para T=128                                  |    |

| Fig 4.27: Resultados finales de la versión Opt-6                                           |    |

| Fig 4.28: Captura de pantalla de función FW_BLOCK (versión Opt-7)                          |    |

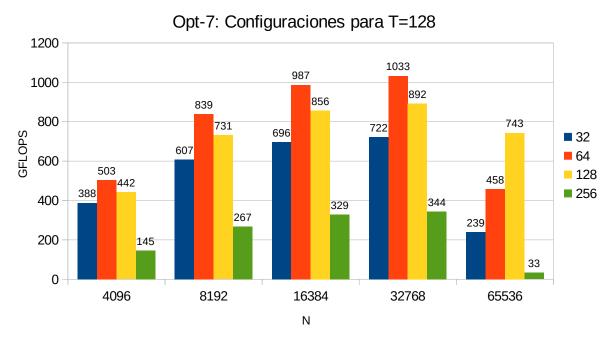

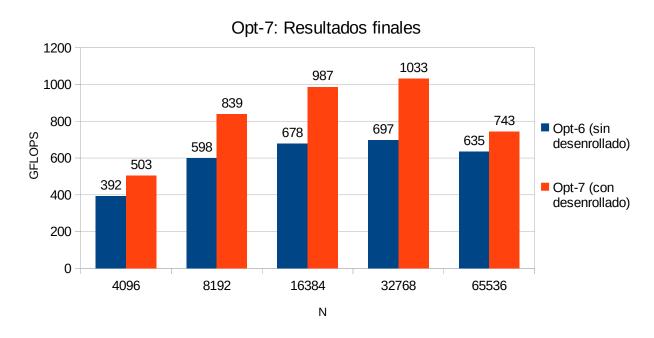

| Fig 4.29: Versión Opt-7. Configuraciones de BS para T=128                                  |    |

| Fig 4 30: Resultados finales de la versión Ont-7                                           | 74 |

| Fig 4.31: Resultados finales de la versión Opt-8                                        | .76 |

|-----------------------------------------------------------------------------------------|-----|

| Fig 4.32: Comparativa de DDR vs MCDRAM utilizando de base la versión Opt-5              |     |

| Fig 4.33: Versión <i>Var-Nopath</i> . Configuraciones de BS para T=128                  | .78 |

| Fig 4.34: Resultados finales de la versión Var-Nopath                                   | .79 |

| Fig 4.35: Versión Var-Dens: Rendimiento arrojado con distintos GD para cada valor de N. | .80 |

| Fig 4.36: Versión Var-Double. Gráfico de comparación de rendimiento float vs double     | .82 |

## Índice de tablas

| Tabla 2.1: Tabla comparativa de memorias MCDRAM y DDR                                 | 9        |

|---------------------------------------------------------------------------------------|----------|

| Tabla 2.2: Modelos de uso de la memoria MCDRAM                                        | 20       |

| Tabla 2.3: Tabla comparativa de técnicas de vectorización                             | 23       |

| Tabla 2.4: Estrategias de alineamiento de datos en memoria                            | 25       |

| Tabla 2.5: Tabla comparativa de técnicas de desenrollado de bucles                    | 27       |

| Tabla 4.1: Primeras versiones de FW implementadas                                     | 35       |

| Tabla 4.2: Version Opt-0 y sus optimizaciones incrementales                           | 35       |

| Tabla 4.3: Experimentos adicionales                                                   | 35       |

| Tabla 4.4: Ejemplo de matriz cuadrada de N=4                                          | 38       |

| Tabla 4.5: Matriz cuadrada de N=4 guardada en un vector de forma ordenada por filas   | 38       |

| Tabla 4.6: Matriz cuadrada de N=4 particionada en bloques de 2x2                      | 47       |

| Tabla 4.7: Matriz cuadrada de N=4 particionada en bloques de 2x2 guardada en un vec   | ctor     |

| siendo ordenada por filas                                                             | 48       |

| Tabla 4.8: Matriz cuadrada de N=4 particionada en bloques de 2x2 guardada en un vec   | ctor     |

| siendo ordenada por filas de bloques, y los bloques internamente siendo ordenados por | r filas. |

|                                                                                       | 48       |

| Tabla 4.9: Segmentos de valores de prueba de BS para los diferentes valores de T      | 56       |

| Tabla 4.10: Herramientas probadas para lograr accesos alineados a memoria             | 65       |

| Tabla 4.11: Versión Opt-8. Resultados de diferentes tipos de afinidad                 | 75       |

| Tabla 4.12: Tabla de resumen de versiones y sus resultados                            | 84       |

# Capítulo 1

## Introducción

En primer lugar, se presenta la motivación de esta tesina (sección 1.1). Luego se enuncian los objetivos y metodología (sección 1.2), y las contribuciones y resultados obtenidos (sección 1.3). Por último, se describe la organización del documento (sección 1.5).

### 1.1. Motivación

El problema del consumo energético se presenta como uno de los mayores obstáculos para el diseño de sistemas de Exa-escala. Por lo tanto, la comunidad científica está en la búsqueda de diferentes maneras de mejorar la eficiencia energética de los sistemas de cómputo de altas prestaciones (HPC por sus siglas en inglés). Una de las estrategias más elegidas en los últimos años ha sido la de incorporar arquitecturas de aceleradores y coprocesadores a los sistemas de supercómputo. La clave en el uso de estos dispositivos se basa en que incrementan el poder computacional de un sistema al mismo tiempo que limitan su consumo de potencia, lo que les permite obtener mejores prestaciones desde la perspectiva energética [1] [2].

Los aceleradores más usados suelen ser las unidades de procesamiento gráfico (GPU por sus siglas en inglés) o los coprocesadores Xeon Phi de Intel. Recientemente, Intel ha presentado la segunda generación de esta clase de aceleradores, con nombre clave Knigths Landing (KNL). Entre sus principales características, se pueden mencionar la gran cantidad de núcleos con soporte para Hyper-Threading, la incorporación de las instrucciones vectoriales AVX-512 y la integración de una memoria de gran ancho de banda.

Desde sus inicios, los grafos y sus algoritmos se han vuelto muy importantes, ya que permiten modelar y resolver problemas de dominios muy diferentes como computación científica, minería de datos, procesamiento de imágenes, ruteo de redes, entre otros. No obstante, estos algoritmos por lo general tienen un costo computacional relativamente elevado, por lo que resulta apropiado ejecutarlos sobre un hardware acorde a las necesidades. Con el objetivo de reducir el tiempo de ejecución al máximo posible, no resulta suficiente simplemente portar la aplicación al nuevo hardware sino que se la debe adaptar de acuerdo a sus características específicas.

Entre los algoritmos de grafos descritos en el párrafo anterior, se encuentra Floyd-Warshall (FW) [3] [4], el cual permite calcular (y hallar) los caminos mínimos entre todos los vértices de un grafo pesado. A este algoritmo en toda su historia se lo ha empleado en ámbitos diversos como el tráfico automovilístico [5], las redes de computadoras [6], bioinformática [7], entre otros. Sin embargo, FW es computacionalmente costoso  $(O(n^3))$  y a medida que el tamaño del

problema escala, el empleo de recursos de cómputo paralelo se vuelve necesario para poder satisfacer sus requerimientos.

De manera de poder computar los caminos mínimos de un grafo con tiempos de respuesta aceptables, resulta necesario desarrollar nuevas soluciones computacionales que sean capaces de aprovechar las arquitecturas HPC actuales.

## 1.2. Objetivos y metodología

El objetivo de esta tesina consiste en evaluar el uso de la arquitectura Xeon Phi KNL para acelerar el algoritmo FW. Para ello se realizarán las siguientes actividades:

- Se estudiará el problema de calcular los caminos mínimos en un grafo y sus requisitos computacionales, en particular siguiendo el algoritmo FW.

- Se examinará la arquitectura de los aceleradores Xeon Phi KNL, los modelos de programación y las técnicas de optimización aplicables.

- Se relevará la bibliografía existente en la temática a partir de la búsqueda en bases de datos especializadas.

- Se diseñarán y desarrollarán diferentes soluciones paralelas al problema estudiado que puedan ejecutarse en aceleradores Xeon Phi KNL, considerando diferentes optimizaciones aplicables.

- Se medirá el rendimiento considerando diferentes escenarios en cada caso y se realizará un análisis de estos.

- Se comparará la propuesta llevada a cabo y sus resultados con otros existentes en la literatura.

## 1.3. Contribuciones

Las contribuciones de esta tesina son las siguientes:

- Una implementación optimizada para computar los caminos mínimos en un grafo de acuerdo con el método FW sobre aceleradores Xeon Phi KNL. Como se mencionó en la sección 1.1, esta implementación podría beneficiar a aplicaciones de ámbitos diversos como el tráfico automovilístico, las redes sociales, las redes de computadoras, la bioinformática, entre otros. Para beneficio de la comunidad científica, esta implementación se encuentra disponible en un repositorio web público [https://github.com/ulisescosti/Tesina-FW-XeonPhiKNL].

- Una evaluación de rendimiento de aceleradores Xeon Phi KNL para computar los caminos mínimos en un grafo de acuerdo con el método FW. Este análisis no sólo permite evidenciar qué optimizaciones tienen mayor impacto en la mejora de rendimiento sino también apreciar el potencial de esta arquitectura para el problema de estudio.

### 1.4. Publicaciones

Esta tesina ha servido como base para la siguiente publicación científica:

"Comparación de Arquitecturas HPC para Computar Caminos Mínimos en Grafos. Intel Xeon Phi KNL vs NVIDIA Pascal", M. Costanzo, E. Rucci, U. Costi, F. Chichizola, y M. Naiouf. En: "Actas del XXVI Congreso Argentino de Ciencias de la Computación (CACIC 2020)" (En prensa).

## 1.5. Organización

En el capítulo 2 se detalla al procesador Xeon Phi KNL, incluyendo su propósito, su arquitectura con la conformación básica de sus núcleos, los conjuntos de instrucciones soportados, así como también los diferentes modos de ejecución y de memoria que provee. Luego se presentan los modelos de programación utilizados en el KNL; y finalmente se detalla una lista de optimizaciones generales que el software debe cumplir si se pretende extraer el mayor rendimiento posible de este procesador.

El capítulo 3 detalla el problema de caminos mínimos de grafos, el algoritmo FW y sus variantes orientadas a la computación paralela.

En la capítulo 4 se presentan las distintas versiones de FW desarrolladas para la arquitectura del Xeon Phi KNL, describiendo cada optimización aplicada y presentando los resultados de rendimiento en las tablas y gráficos correspondientes.

Por último, en el capítulo 5 se presentan las conclusiones y trabajos futuros.

# Capítulo 2

# Intel Xeon Phi Knighs Landing

En este capítulo se comienza presentando la organización y arquitectura del procesador (sección 2.1). Luego se enuncian los modelos de programación (sección 2.2), optimizaciones de software para aprovechar el potencial del procesador (sección 2.3), y por último, un resumen del capítulo (sección 2.4).

## 2.1. Organización y arquitectura

El procesador Intel Xeon Phi Knights Landing (KNL) es un procesador del tipo *many-core*, es decir, a diferencia de un *multi-core* tradicional, éste dispone de núcleos más simples pero en una cantidad mucho mayor. Está orientado y optimizado para un alto nivel de paralelismo explícito, a expensas de proveer menor rendimiento en la ejecución de un único hilo.

A diferencia de otros tipos de procesadores *many-core y* GPUs, los Xeon Phi tienen una ventaja fundamental al mantener la arquitectura y conjunto de instrucciones x86. Ésto permite facilitar el desarrollo de software al permitir utilizar las herramientas de paralelización pre-existentes, tales como OpenMP y MPI, y siendo compatibles con cualquier librería y ejecutable x86 preexistente. El objetivo del Xeon Phi es competir en el área de HPC al proveer una potencia de cómputo de paralelismo masivo comparable al de una GPU de alto rendimiento, pero reduciendo el esfuerzo de programación casi como si se tratase de un *multi-core* tradicional.

## **2.1.1. Origen**

El Xeon Phi KNL tiene una arquitectura del tipo Intel Many Integrated Core (MIC), la cual nació siguiendo la filosofía de Larrabee, una arquitectura experimental de GPUs de Intel basada en x86. Si bien Larrabee tenía inicialmente planificado su primer producto comercial para ser lanzado 2010, finalmente esto no se cumplió. Todo el proyecto terminó siendo cancelado debido a continuos retrasos en el desarrollo y por resultados iniciales de rendimiento muy por debajo de los esperados. No obstante, Larrabee sirvió de base para desarrollos futuros de otras arquitecturas del tipo *many-core* como es el caso de MIC.

La arquitectura MIC reutilizó gran parte de la investigación de Larrabee, heredando de ésta elementos tales como las unidades de procesamiento vectorial (unidades SIMD) de 512 bits, y el sistema de coherencia de caché, entre otros. La principal diferencia con Larrabee, es que un

procesador de arquitectura MIC ya no es más una GPU, sino que se trata más bien de un coprocesador orientado fuertemente a HPC.

El primer procesador comercial de arquitectura MIC fue el Intel Xeon Phi - Knights Corner (KNC), lanzado en 2013. Éste, al igual que su predecesora arquitectura Larrabee, tiene a sus núcleos basados en la arquitectura P5 (la de los primeros Pentium de los años 90), es decir, se trata de núcleos superescalares con ejecución en-orden. También se mantuvo el agregado de una unidad SIMD de 512 bits, la implementación de Hyper-Threading de 4-vías (capaz de ejecutar simultáneamente cuatro hilos por núcleo), y la extensión de la arquitectura de x86 a x86-64. El procesador, según el modelo, posee entre 57 y 61 núcleos, interconectados por un bus en anillo, y funcionan a una frecuencia de entre 1053 y 1333MHz. Con Hyper-Threading activado, un modelo de 61 núcleos es capaz de ejecutar 244 hilos en simultáneo. Todos los Xeon Phi KNC salieron al mercado como coprocesadores en formato de tarjeta aceleradora, en su mayoría con interfaz PCI-Express 2.0 16x. Según el modelo en particular, el KNC posee entre 6 y 16GB de memoria GDDR5 (memoria de gran ancho de banda, común en tarjetas gráficas).

En 2016, con el avance en el proceso de litografía de 22nm a 14nm, se lanzó un nuevo Xeon Phi, llamado Knights Landing (KNL), el cuál no solo elevó la cantidad de transistores de 5 mil millones a 8 mil millones (manteniendo un tamaño similar de pastilla), sino que además se implementaron cambios profundos en la arquitectura con el objetivo de aumentar fuertemente el rendimiento *single-thread*.

# 2.1.2. Novedades de KNL con respecto a las versiones anteriores de Xeon Phi

Si bien con Knights Landing casi se duplicó la cantidad de transistores con respecto a Knights Corner, esto no se tradujo a duplicar también la cantidad de núcleos; ya que solo pasaron de 61 (en *KNC*) a 72 con KNL en los respectivos modelos tope de gama. Esto se debe a que los diseñadores de la arquitectura más bien priorizaron incrementar el valor de IPC\*¹, a modo de poder cumplir el objetivo de mejorar el rendimiento *single-thread* (mono-hilo). En otras palabras, los circuitos extra provistos por el salto a los 14nm, fueron utilizados en mayor medida para incrementar la complejidad y potencia de los núcleos mas que para aumentar la cantidad de los mismos.

Para lograr el objetivo de incrementar sustancialmente el rendimiento *single-thread*, se efectuó un fuerte rediseño de la arquitectura a nivel núcleo. Éstos, ahora están basados en la arquitectura Silvermont en lugar de la P5, por lo que se trata de núcleos mucho más complejos, que implementan ejecución fuera de orden de ancho 2 (se traduce en más IPC). Ésto, sumado al agregado de una segunda unidad de procesamiento SIMD de 512 bits, y al aumento de

<sup>1</sup> IPC = Instructions per cycle (Instrucciones por ciclo). Define la cantidad de instrucciones de un hilo que el procesador es capaz de ejecutar en paralelo en cada ciclo de reloj. El IPC a fines prácticos le da "un peso" al valor de frecuencia del procesador, que es el que determina la cantidad de ciclos por segundo que tiene su reloj. Por ejemplo, un procesador con IPC alto y frecuencia baja, podría en muchos casos ser más rápido que otro procesador que funciona a altas frecuencias, pero con un IPC mucho más bajo. Un ejemplo muy famoso de esto es la rivalidad de los años 2000-2006 entre los procesadores Athlon 64 de AMD (relativa baja frecuencia, alto IPC) y los Pentium 4 de Intel (muy alta frecuencia para la época, pero muy bajo IPC).

frecuencia de 1333MHz (con Knights Corner) a 1700MHz, se logra al menos el doble de rendimiento *single-thread* con respecto a KNC.

Otra novedad de KNL es que no requiere de un procesador *host* como sí lo hacía KNC, ya que KNL es capaz de comportarse por sí mismo como un procesador *host* autónomo; es decir, es capaz de bootear sistemas operativos, conectarse directamente a una red (ya sea Ethernet, Infiniband, o similar), y no sufre del *overhead* del *off-loading* que sí está presente en los KNC y en las GPU, en los cuales se necesita inevitablemente transferir datos desde y hacia la placa PCI-Express. Inicialmente se iban a lanzar también modelos de KNL en formato PCI-Express como exclusivamente coprocesadores, pero fueron cancelados y solo salieron a la venta los modelos de procesadores autónomos. Los KNL, en lugar de venir con memoria GDDR5 (presente en los KNC), vienen con una memoria de 16GB de alto ancho de banda llamada MCDRAM, con sus chips integrados en la misma plaqueta del procesador. Además de la MCDRAM, el KNL (como cualquier otro procesador autónomo) utiliza directamente a la memoria DDR RAM, que en este caso, se trata de 6 canales de DDR4 que soportan un máximo de 384GB. Como resultado de todos estos cambios, el Xeon Phi KNL ahora ofrece picos de rendimiento para punto flotante de alrededor de 3 TFLOP/s con doble precisión y 6 TFLOP/s con simple precisión.

Otra característica de KNL es que, a diferencia de KNC, éste mantiene la compatibilidad con los sets de instrucciones de procesamiento vectorial *legacy* como las SSE, y las AVXx; e introduce AVX-512, un conjunto de instrucciones vectoriales de 512 bits que son arquitectónicamente consistentes con las anteriores AVX y AVX2 de 256 bits. KNC proveía también un conjunto de instrucciones vectoriales de 512 bits pero era uno específico del procesador, no pensado como una evolución natural de AVX2. Todas estas características de retrocompatibilidad de los sets de instrucciones, sumado a que KNL se trata de un procesador x86-64 capaz de funcionar como un procesador *host* autónomo, le permite brindar la compatibilidad binaria con programas previamente compilados no solo para procesadores Xeon estándar, sino que también es capaz de ejecutar cualquier programa o librería *legacy* compilados para las arquitecturas x86 o x86-64 genéricas.

## 2.1.3. Unidad de replicación escalable de la arquitectura

## Organización en tiles

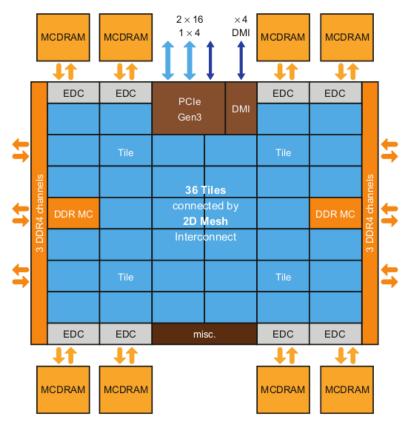

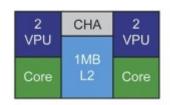

La unidad básica de replicación en la arquitectura del Xeon Phi KNL es el *tile* ("baldoza" / "azulejo"). Como se muestra en la figura 2.2, un *tile* está conformado por dos núcleos, dos unidades de procesamiento vectorial por núcleo, y 1MB de caché L2 compartida entre ambos núcleos. Cada pastilla del KNL cuenta con 38 *tiles*, de los cuales a lo sumo 36 están activos (en los modelos tope de gama); los otros *tiles* restantes se desactivan por motivos de eficiencia en el proceso de fabricación. En la figura 2.1 se muestra un diagrama de bloques del paquete, donde se puede apreciar la distribución de los tiles a lo largo de todo el chip, los controladores de memoria, y los integrados de MCDRAM.

Fig 2.2: Diagrama de bloques de un tile.

Fuente: FIG 2.3 [8, p. 18]

Fig 2.1: Diagrama de bloques del paquete del KNL (CPU).

Fuente: FIG 2.2 [8, p. 18]

#### Interconexión de tiles

Los *tiles* se encuentran interconectados por una red de interconexión de tipo *mesh* (malla) 2D, que implementa coherencia de caché con directorio distribuido. La malla interconecta filas y columnas de *tiles* con un protocolo de ruteo estático, con el cual, cada transacción de memoria viaja primero verticalmente hasta llegar a la fila buscada, y luego viaja horizontalmente hasta llegar al tile destino. Este sistema es mucho más eficiente y escalable que el sistema de interconexión de anillo 1D de Knights Corner, por lo que provee un mayor ancho de banda y a la vez menor latencia.

## 2.1.4. Modos de ejecución (modos cluster)

#### Introducción

La malla que interconecta los tiles del KNL se puede configurar en tres modos de ejecución distintos: A*ll-to-all*, Quadrant, y Sub-NUMA Clustering (SNC). Estos modos particionan al procesador en regiones virtuales separadas estableciendo cierta afinidad de direcciones de memoria con la partición de la malla que le corresponde. Esto no es un impedimento para

mantener la coherencia de caché en todo el procesador a lo largo de todas las particiones, cosa que ocurre independientemente del modo cluster elegido.

El KNL implementa la coherencia de caché L2 con directorio distribuido y protocolo MESIF. El directorio se encuentra distribuido entre los *Cache/Home Agent* (CHA). Cada *tile* alberga uno de estos agentes de caché.

Es importante remarcar que cualquier software compilado para x86 puede ejecutarse en cualquiera de los modos cluster. No obstante, para ganar rendimiento aprovechando al máximo las características del KNL, normalmente es deseable efectuar modificaciones al código si no fue diseñado puntualmente para esta arquitectura. La novedad es que no solo el software es el que puede modificarse para aprovechar las características del procesador, sino que con KNL, el procesador también puede adaptarse al software al poder elegir manualmente el modo cluster a utilizar según las características del software que se desea ejecutar.

#### Modo All-to-all

Es el modo cluster más lento, pero el único disponible cuando los módulos de memora DDR no son idénticos en capacidad. En este modo no hay afinidad entre los *tiles*, agentes de caché y controladores de memoria. Esta carencia de afinidades es lo que brinda la flexibilidad necesaria para mantener la compatibilidad con canales DDR asimétricos. No obstante, con este esquema se pierde rendimiento, ya que las transacciones por fallo de caché L2 recorren distancias más largas en promedio, y por consiguiente, pueden tardar más tiempo en resolverse. La única ventaja de este modo cluster sobre el resto es que soporta cualquier configuración de módulos DDR.

### **Modo Quadrant**

Es el modo cluster por defecto, pero requiere que se instalen módulos DDR de la misma capacidad. Si se detecta una asimetría en los canales de memoria, el modo *All-to-all* será seleccionado automáticamente.

Con el modo *Quadrant*, el chip queda dividido lógicamente en cuatro cuadrantes, y se establece una afinidad entre los agentes de caché y los controladores de memoria. Esto hace que los fallos de caché L2 tarden menos tiempo en resolverse en comparación al que requerirían en el modo *All-to-all*.

#### Modo SNC-4

El modo SNC implementa una afinidad entre los tres elementos vinculados en las transacciones en los fallos de caché L2; es decir, el *tile*, el agente de caché y el controlador de memoria. Esto permite dividir al chip en cuatro cuadrantes como cuatro clusters NUMA\*¹. En este modo, ante un fallo de caché L2, si la posición de memoria se encuentra en el mismo cuadrante, queda

<sup>1</sup> NUMA es un diseño de memoria, en el cual a diferencia del esquema UMA tradicional, los accesos tienen determinísticamente un tiempo de acceso mejor o peor según en qué zona de memoria se encuentre el dato a operar; por lo que el software que corre en un sistema NUMA debe hacer un uso discrecional de las zonas rápidas y lentas de la memoria para lograr tiempos de acceso óptimos.

garantizado que el fallo se resolverá internamente en el mismo cuadrante, logrando así los tiempos de acceso más óptimos de los tres modos cluster.

Si el software no está optimizado para NUMA y accede frecuentemente a zonas de memoria "lejanas" (pertenecientes a otros cuadrantes), muy probablemente se obtenga menos rendimiento con SNC-4 que con *Quadrant*.

#### **Modo Hemisphere y SNC-2**

Estos modos son simples variaciones de los modos *Quadrant* y SNC-4 respectivamente. En *Hemisphere* en lugar de dividir el chip en cuatro cuadrantes, se divide en dos hemisferios. De igual manera, con SNC-2 el sistema se divide en dos clusters NUMA en lugar de cuatro. En estos modos se obtiene menos rendimiento que con *Quadrant* y SNC-4, pero siguen teniendo menor latencia y mayor ancho de banda que el modo *All-to-all*.

## 2.1.5. Tipos de memoria (MCDRAM y DDR)

#### Memoria DDR

Al ser el Xeon Phi KNL un procesador autónomo, como cualquier *multi-core* tradicional, puede acceder a la memoria DDR de gran capacidad. El KNL soporta 6 canales DDR4, con un ancho de banda combinado de aproximadamente 90 GB/s, y con una capacidad máxima total de 384GB, dependiendo del tamaño de los módulos instalados.

#### Memoria MCDRAM

Además de la memoria DDR, el procesador KNL cuenta con una memoria de 16GB de alto ancho de banda llamada MCDRAM. Esta memoria complementaria le brinda al KNL la posibilidad de tener un ancho de banda similar al de las GPUs, sin tener que sacrificar capacidad para lograrlo (ventaja clave de poder acceder a ambas memorias).

Los chips de la MCDRAM (de 2 GB cada uno en este caso) están integrados en el paquete del procesador; es decir, están soldados en la misma plaqueta; y el ancho de banda combinado de los ocho chips de MCDRAM es superior a los 450GB/s. Estas diferencias técnicas se presentan en la tabla 2.1.

### Tabla comparativa

|        | Capacidad   | Ancho de banda | Latencia en idle |

|--------|-------------|----------------|------------------|

| MCDRAM | 16GB        | Hasta 450GB/s  | ~ 150ns          |

| DDR    | Hasta 384GB | Hasta 90GB/s   | ~ 125ns          |

Tabla 2.1: Tabla comparativa de memorias MCDRAM y DDR.

Fuente: FIG 4.15 [8, p. 82]

#### 2.1.6. Modos de memoria

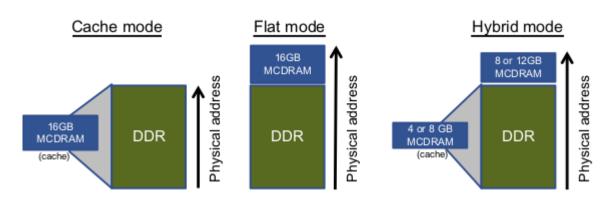

La memoria puede ser configurada en tiempo de booteo en uno de los siguientes modos:

- I. Modo *Cache*: la MCDRAM se comporta como una caché de la DDR.

- II. <u>Modo *Flat* (plano)</u>: la MCDRAM es tratada como una memoria estándar en el mismo espacio de direcciones de la DDR.

- III. <u>Modo *Hybrid* (híbrido)</u>: una porción de la MCDRAM funciona como caché de la DDR, y la porción restante queda en la modalidad *flat*.

Fig 2.3: *Gráfico representativo de los tres modos de memoria del KNL.*

Fuente: FIG 4.13 [8, p. 79]

A continuación se describen los modos de memoria más en detalle:

#### **Modo Cache**

En este modo, la memoria MCDRAM es configurada y administrada por hardware como una caché de la memoria DDR. Es el modo de memoria ideal para ejecutar software *legacy*, ya que le permite gozar del ancho de banda de la MCDRAM mientras ésta es usada de forma transparente, sin tener que solicitarla por ningún medio. En este modo, el software utiliza la DDR como si se tratase de la única disponible, y es el sistema de memoria el que se encarga de cachearla con la MCDRAM automáticamente, lo que efectivamente le brinda la transparencia requerida. Para gozar de los beneficios de este modo, no se requiere de ninguna modificación en el código fuente ni ninguna modificación en los parámetros del ejecutable. Para la mayoría de las aplicaciones, este será el modo de memoria más apropiado. No obstante, para algunas aplicaciones con naturaleza "poco amigable" con las memorias caché (es decir, con baja tasa de *hits*), probablemente puedan obtener mayor rendimiento con los otros dos modos de memoria.

#### **Modo Flat**

El modo *flat* permite que el sistema operativo vea a la memoria MCDRAM como otra memoria direccionable, es decir, como un nodo NUMA separado. Esto permite que por software, selectivamente, se pueden utilizar a ambas memorias (DDR y MCDRAM) haciendo uso explícito de ellas. Por defecto, todos los datos se ubicarán en la DDR, reservando a la MCDRAM como un recurso preciado, para que el programador ubique en la misma solo los datos más críticos con respecto a la demanda de ancho de banda. El resultado, es que si el programador utiliza la MCDRAM correctamente, el rendimiento será más consistente que el obtenido con el modo caché, al no depender de ninguna tasa de *hits*.

Para elegir el tipo de memoria a utilizar hay disponibles diversos métodos y herramientas. Una de las herramientas más comunes utilizada para manejar la MCDRAM es la librería Memkind, la cual permite definir explícitamente en el código (de forma bastante amigable) cuándo reservar espacio en memoria DDR y cuándo en la MCDRAM. No obstante, para mantener la portabilidad del software *legacy*, también se puede definir el tipo de uso que se le dará a la memoria MCDRAM antes de la carga de un programa; permitiendo así que dicho programa legacy pueda hacer un uso directo de la memoria MCDRAM en modo *flat* sin ser "consciente" de ello.

#### Modo hybrid

En el modo *hybrid*, una parte de la memoria MCDRAM se utiliza como caché y la otra parte se utiliza como memoria *flat*, por lo que se trata de una combinación entre ambos modos de memoria. En este modo, la parte de la MCDRAM que se utiliza como *flat* queda en un nodo NUMA separado, mientras que la parte restante queda como caché de toda la memoria DDR.

Este modo es útil para aplicaciones que se benefician del *caching* gracias a una alta tasa de *hits*, y que a su vez pueden potencialmente mejorar aún más su rendimiento al utilizar selectivamente la MCDRAM.

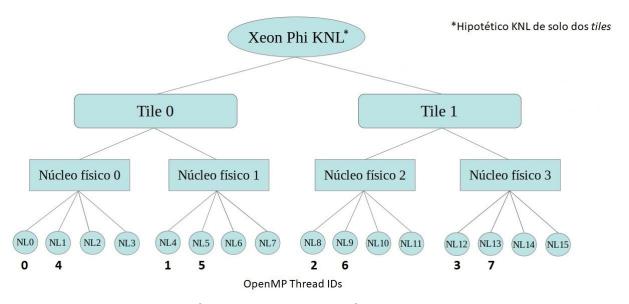

## 2.1.7. Simultaneous Multi Threading (SMT)

El Xeon Phi KNL implementa la tecnología SMT bajo el nombre comercial Hyper-Threading, la cual le permite ejecutar múltiples hilos simultáneamente en un mismo núcleo. Esta tecnología se aprovecha de las arquitecturas superescalares de los procesadores, para que estos en vez de captar siempre instrucciones de un mismo hilo, ahora lo puedan hacer con instrucciones de distintos hilos simultáneamente, sin que esto implique ningún tipo de *context switch*. El hardware extra requerido para que un procesador implemente esta tecnología es mínimo, por lo que básicamente, SMT permite explotar los recursos preexistentes de los procesadores, algo que en muchos casos no es posible de lograr con la ejecución de un único hilo por núcleo.

La mejora de rendimiento obtenida con el uso de SMT es algo dependiente de las características de la aplicación a correr, pudiendo obtener mejoras de rendimiento del orden del 40%, no obtener mejora alguna, o incluso tener un impacto negativo sustancial en el rendimiento.

Si bien la tecnología SMT no aumenta la cantidad real de núcleos, los sistemas operativos ven a un procesador con SMT como si tuviera una cantidad de núcleos igual a la cantidad de hilos que es capaz de ejecutar en simultaneo. Por ejemplo, a un procesador de 8 núcleos con SMT de dos hilos por núcleo, los sistemas operativos lo verán como un procesador de 16 núcleos. Aquí entran en juego las distinciones "núcleo lógico" y "núcleo físico", utilizadas frecuentemente para diferenciar los núcleos que el sistema operativo ve (núcleos lógicos) con los núcleos reales del procesador (núcleos físicos).

## 2.2. Modelos de programación

Los modelos de programación soportados por el KNL varían según si éste es utilizado como procesador nativo o como coprocesador. No obstante, en esta tesina se hará hincapié en la configuración del KNL como procesador nativo, ya que se trata del modo más ampliamente utilizado en general, y es el que será empleado a lo largo del desarrollo de este trabajo.

Un KNL como procesador nativo soporta los mismos modelos de programación disponibles para cualquier *multi-core* del mercado, ya sea OpenMP, MPI\*¹, o el híbrido MPI+X (por ejemplo, MPI + OpenMP), siendo en general cada uno de estos más afín a un determinado modo cluster y modo de memoria. En este trabajo, el modelo de programación a utilizar será el de OpenMP, por lo que de aquí en adelante se hará principal énfasis en éste último.

## 2.2.1. OpenMP

OpenMP es un estándar para la programación paralela en memoria compartida. Se compone de un conjunto de directivas, un conjunto de variables de entorno y un conjunto de funciones de librería. Su origen radica en la necesidad de poder desarrollar programas paralelos escalables a un bajo costo de programación. En ese sentido, se dice que OpenMP sigue una filosofía de diseño incremental, ya que no requiere escribir un código "desde cero".

OpenMP se basa en el modelo *Fork-Join*. Un programa paralelo implementado con OpenMP arranca con un hilo maestro, y éste al llegar al primer bloque paralelo crea los correspondientes hilos *workers* (*Fork*). Estos hilos trabajarán concurrentemente dentro del bloque paralelo, y en el caso en que haya un *for* paralelo (o una sección) repartirá la carga del mismo entre ellos. Al final de cada *for* paralelo (o sección paralela) hay una barrera implícita, donde cada hilo se duerme esperando a que el resto termine su trabajo. Luego, vuelven a repartirse la carga en caso de que haya consecutivamente otro *for* o sección paralela. Una vez que se termina la ejecución de todo el bloque paralelo, se eliminan los hilos *workers* (*Join*), para luego continuar la ejecución del hilo maestro en solitario. Cuando el hilo maestro llega otra vez a un bloque paralelo, nuevamente se vuelven a crear los hilos *workers* necesarios (*Fork*), y otra vez se cumple el mismo ciclo descrito anteriormente por cada bloque paralelo encontrado en el programa hasta su finalización.

<sup>1</sup> MPI: es un estándar de pasaje de mensajes para programas paralelos distribuidos.

#### Directivas básicas

A continuación se listan algunas de las directivas de OpenMP\*¹ para C y C++ más básicas utilizadas a lo largo de este trabajo.

#### #pragma omp parallel

- Define un bloque de código que se va a ejecutar en paralelo.

- Se ubica una línea antes del comienzo del bloque.

- Cuando el bloque se ejecuta, al comienzo se crean los hilos en la cantidad definida en la variable de entorno OMP\_NUM\_THREADS. Al finalizar la ejecución del bloque se matan dichos hilos.

#### #pragma omp for

- Se utiliza dentro de un bloque *parallel*, ubicándose una linea antes del comienzo de un *loop* (*for* en C y C++).

- Indica al compilador que debe paralelizar (a nivel de *threads*) a un *loop* determinado. Si hay *loops* anidados dentro, estos se ejecutaran secuencialmente dentro del contexto de cada hilo.

- Reparte las iteraciones del *loop* entre los distintos hilos correspondientes al bloque *parallel*. Esta repartición de trabajo entre hilos por defecto es estática, pero puede hacerse dinámica, con distintas sub-variantes según ciertos parámetros opcionales de la directiva.

- Al final del *loop* paralelizado, por defecto se deja un *join* (barrera) implícito.

#### Cláusulas de visibilidad de datos

#### private(<lista de variables>)

Las variables definidas en esta cláusula se guardan en la memoria *stack* local de cada hilo, por lo que estos llevan una copia local de cada una de las variables. Es la cláusula por defecto para la variable utilizada como índice de un *loop* paralelizado.

### firstprivate(<lista de variables>)

Similar a *private*, pero las variables primero se inicializan con el valor definido previamente en el hilo maestro.

#### shared(<lista de variables>)

Cláusula por defecto de todas las variables (excepto la variable usada como índice de un *loop* paralelizado), estas permanecerán en el contexto global, por lo que serán utilizadas de forma compartida por todos los hilos del bloque paralelo.

Para más información sobre las diferentes directivas de OpenMP: [https://www.openmp.org]

## 2.3. Optimizaciones

Es importante remarcar que si se parte de una aplicación no optimizada para la ejecución paralela, centrarse desde el "minuto cero" en la optimización fina para la arquitectura del KNL no suele ser lo ideal. Generalmente resulta más efectivo comenzar con las técnicas de paralelización y optimización genéricas para *multi-cores*; y por lo tanto, demás está decir que también se deben tener en cuenta las optimizaciones respectivas desde el punto de visa de la ejecución individual de un hilo. Habiendo dicho esto, ahora partiendo de una aplicación optimizada para *multi-cores* en general, se puede empezar a introducirse de a poco en las particularidades mas finas de la arquitectura del KNL. Primero se puede comenzar eligiendo el modo cluster y el modo de memoria más apropiados según las características del problema, como se verá a continuación.

#### 2.3.1. Modos Cluster

Se puede dividir a los modos cluster en dos grupos según cómo los diferentes modelos de programación se adecúan a ellos:

#### Modos SNC-4 y SNC-2

Con los modos SNC es posible obtener más rendimiento que con *Quadrant* en aplicaciones del tipo "*NUMA aware*"; es decir, aplicaciones ya optimizadas para NUMA. Estas aplicaciones tienen un gran potencial de lograr mejor rendimiento con estos modos cluster, gracias a utilizar discrecionalmente los accesos a memoria "cercanos" y "lejanos", buscando así maximizar las comunicaciones internas (accesos "cercanos") y minimizando las comunicaciones entre distintos clusters NUMA (accesos "lejanos").

Es importante remarcar que para un núcleo, lo que determina si un dato va a estar en "memoria cercana" o en "memoria lejana" con respecto a él, es si fue desde ese mismo núcleo (o desde otro de su mismo cuadrante) donde se accedió por primera vez al dato en cuestión. Si el dato fue accedido primero por un núcleo perteneciente otro cuadrante diferente, entonces dicho dato quedará en "memoria lejana" desde su punto de vista. Por este motivo, es muy importante analizar cómo las aplicaciones inicializan sus datos. Se deben evitar comportamientos como el de un proceso/hilo maestro que se encarga de inicializar las estructuras en memoria para todos los hilos de los diferentes cuadrantes; esto es algo que no debe suceder si se espera obtener buen rendimiento con los modos cluster SNC. También puede ser perjudicial para el rendimiento en los modos cluster SNC si un hilo es cambiado de núcleo por el sistema operativo y termina en un núcleo de un cuadrante distinto, por lo que toda su memoria "cercana" pasaría inmediatamente a estar en memoria "lejana" desde su punto de vista. Esto se soluciona estableciendo una afinidad de hilos con núcleos, como se verá más adelante en la sección 2.3.4.

Las aplicaciones del tipo MPI / MPI+X que utilizan 4 procesos por nodo, o bien un múltiplo de 4 procesos por nodo, tienen naturalmente grandes probabilidades de obtener mejor rendimiento con SNC-4 que con el resto de los modos cluster. Ademas de coincidir (o ser múltiplo) la cantidad de procesos por nodo con la cantidad de clusters NUMA que habría disponibles con

SNC-4, se le suma el hecho de que normalmente este tipo de aplicaciones suelen estar pensadas desde cero con la correspondiente minimización de la comunicación entre procesos (accesos lejanos), en favor de las comunicaciones internas entre hilos de un mismo proceso (accesos cercanos). Del mismo modo (y por descarte), las aplicaciones con 2 procesos por nodo, o un múltiplo de 2 procesos por nodo, tienen chances de ejecutarse más rápido con SNC-2 que con el modo *Quadrant*.

Para aplicaciones MPI que no tienen una cantidad adecuada de procesos por nodo y/o que no localizan suficientemente las comunicaciones, probablemente corran mejor con los modos *Quadrant* o *Hemisphere*.

#### Modos Quadrant, Hemisphere y All-to-all

Desde el punto de vista del software, con estos modos cluster, el KNL se comporta como si se tratase de un único *multi-core*. De hecho, un programa implementado con cualquier modelo de programación utilizado para *multi-cores*, puede correr en el KNL sin más modificaciones, y aún así esperar tener buenos resultados de rendimiento. Estos tres modos cluster son transparentes desde el punto de vista del software; por lo que para una aplicación, lo único que puede variar es el rendimiento obtenido con cada uno de ellos.

#### 2.3.2. Modos de memoria

La decisión entre elegir el modo de memoria *cache* o el modo *flat*, dependerá principalmente de si las aplicaciones a correr son "*cache-friendly*" o no. Si una aplicación ya de por sí es de naturaleza "*cache-friendly*", entonces probablemente corra mejor con el modo de memoria *cache*; mientras que las aplicaciones restantes probablemente puedan obtener más rendimiento con los modos *flat* y *hybrid*.

## 2.3.3. Elección de cantidad de hilos por núcleo (SMT)

Si bien la estrategia de utilizar la mayor cantidad de núcleos posibles suele ser la ideal para el rendimiento, una vez que todos ellos tienen un hilo asignado, al agregarle más podría no mejorar el tiempo de ejecución, e inclusive hasta podría empeorarlo. Esto es algo muy dependiente de la aplicación, su granularidad y la "densidad" de accesos a memoria que efectúe cada hilo. No hay una receta maestra que determine la cantidad de hilos por núcleo óptima, por lo que al final de cuentas lo mejor es parametrizar dicha cantidad de hilos a utilizar, para luego probarlas empíricamente hasta dar con la óptima para una aplicación determinada.

Es esperable que una configuración de 3 hilos por núcleo no sea la más adecuada; en muy pocos casos con ésta se obtiene más rendimiento que con el resto de las configuraciones. Esto se debe a que en el KNL los recursos del núcleo (que se comparten dinámicamente entre los hilos) se pueden dividir en dos o en cuatro, pero no en tres. Es por este motivo que cada hilo bajo una configuración de tres hilos por núcleo utilizará un cuarto de los recursos del núcleo, en lugar de un tercio como intuitivamente uno podría creer [8, p. 108].

#### 2.3.4. Afinidad de hilos con núcleos

El rendimiento de una aplicación puede variar sensiblemente según cómo sus hilos se distribuyen entre los núcleos de los procesadores. Una aplicación paralela habitualmente variará su rendimiento según cuán bien su distribución de hilos aproveche los recursos de cómputo del procesador, así como también según cómo dicha distribución de hilos hace uso de los distintos niveles compartidos de memoria caché. A continuación se detallarán ambos escenarios, enumerándolos como A y B, los cuales serán referenciados luego:

- a) Aprovechamiento óptimo de los recursos de cómputo: si una aplicación trabaja con menos hilos que núcleos físicos disponibles, es deseable que dichos hilos se distribuyan de tal manera que la mayor cantidad posible de núcleos físicos tenga al menos un hilo que ejecutar\*<sup>1</sup>.

- b) <u>Aprovechamiento de la memoria caché</u>: los hilos que comparten datos entre sí probablemente se verán beneficiados si se ejecutan en núcleos lógicos pertenecientes al mismo núcleo físico (comparten caché L1), o bien en núcleos físicos distintos pero del mismo *tile* (comparten caché L2 en el caso del KNL).

Si bien la estrategia A en general tiene mucho más peso en el rendimiento que la B, esta última también se toma en consideración en diversas configuraciones, como se verá más adelante.

El sistema operativo es el que por defecto se encarga totalmente de distribuir los hilos entre los núcleos del procesador, aunque este ligamiento también puede definirse manualmente. Asimismo, es posible utilizar herramientas más amigables que hacen este trabajo por nosotros, permitiendo elegir el patrón de distribución de hilos con unos simples parámetros, y luego la herramienta se encarga de implementar el ligamiento de forma transparente al usuario. Existen múltiples herramientas que brindan este tipo de soluciones. No obstante, en este documento se va a hacer principal énfasis en la Interfaz de Afinidad de Hilos de Intel, la cual será la herramienta a utilizar a lo largo de este trabajo.

## Interfaz de Afinidad de Hilos (Intel)

Esta herramienta provee la variable de entorno KMP\_AFFINITY, la cual permite pasarle una aglomeración de parámetros (previo a la ejecución de un programa), para que la interfaz se encargue de efectuar el ligamiento de hilos con núcleos siguiendo el patrón que el usuario (programador) desee. El principal parámetro a utilizar es el tipo de afinidad, el cual soporta distintos valores enumerativos, siendo los más relevantes: balanced, scatter y compact.

## Tipos de afinidad

**scatter**: lleva la estrategia A al máximo, ubicando los hilos de la forma mas dispersa posible a lo largo de todo el sistema. Suele ser la mejor opción para plataformas *multi-socket*. En la figura 2.6 se presenta un ejemplo de uso de este tipo de afinidad para una configuración de 8 hilos, en un hipotético Xeon Phi KNL de solo dos *tiles*.

Recordar que los recursos de cómputo se comparten entre los hilos de un mismo núcleo físico; por lo que dejar núcleos físicos enteros sin utilizar, representa un importante desaprovechamiento de recursos de hardware.

Fig 2.4: Ejemplo de distribución de hilos con tipo de afinidad "scatter"

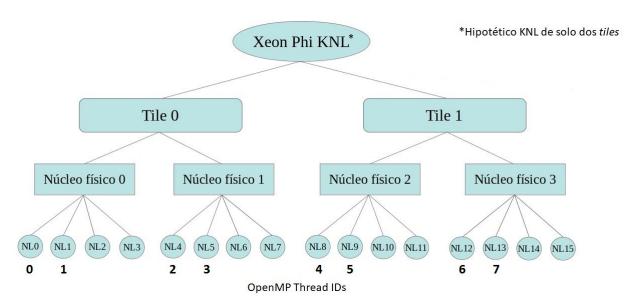

**compact**: Lleva la estrategia B al máximo, ubicando los hilos con ID\*¹ consecutivos de forma ordenada entre núcleos lógicos consecutivos. De esta forma, se maximiza el uso compartido colaborativo de los diferentes niveles de caché. No obstante, este tipo de afinidad tiene fuertes perdidas de rendimiento si la cantidad total de hilos no alcanza para dar trabajo a todos los núcleos físicos del procesador. En la figura 2.5 se ejemplifica dicho escenario, donde la cantidad de hilos no es suficiente para aprovechar todos los núcleos físicos del procesador utilizando este tipo de afinidad.

Fig 2.5: Ejemplo de distribución de hilos con afinidad "compact"

<sup>1</sup> *Thread ID* de hilos de OpenMP en el contexto de OpenMP. Es decir, <u>no</u> se trata del *thread ID* de los hilos a nivel del kernel del sistema operativo.

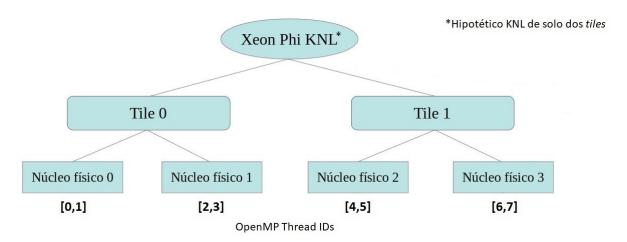

**balanced**: es una solución híbrida que toma lo mejor de s*catter* y *compact*. Primero reparte los hilos de la forma más dispersa posible entre los distintos núcleos físicos hasta tener un hilo por núcleo físico (estrategia A). Luego asigna los restantes hilos a los núcleos lógicos que queden disponibles, de forma tal que los hilos que comparten cada núcleo físico sean de IDs consecutivos (estrategia B). Esta solución no está disponible para plataformas *multi-socket*. En la figura 2.7 se presenta un ejemplo con este tipo de afinidad.

Fig 2.6: Ejemplo de distribución de hilos con afinidad "balanced"

#### Granularidad

**thread/fine**: cada hilo se liga individualmente con un núcleo lógico en particular, de modo que un hilo no puede cambiar de núcleo (ni físico ni lógico) en tiempo de ejecución. Los ejemplos de las figuras 2.5, 2.6 y 2.7 corresponden a este tipo de granularidad.

**core**: es la granularidad por defecto. En esta configuración, grupos de hilos se asocian a núcleos físicos, de modo que los hilos de cada grupo puedan "flotar" entre los núcleos lógicos que comparten el mismo núcleo físico. De esta forma, luego de un *context switch* de un hilo, su ejecución puede reanudarse inmediatamente en cualquiera de los otros tres núcleos lógicos "vecinos". En la figura 2.7 se presenta un ejemplo de afinidad *balanced* con granularidad *core*.

Fig 2.7: Ejemplo de distribución de hilos con granularidad "core" y tipo de afinidad "balanced"

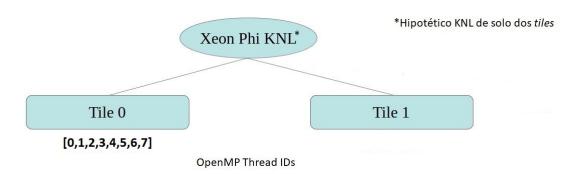

<u>tile</u>: implementa la misma idea de la granularidad *core* pero llevada al nivel del *tile*. Es decir, liga grupos de hilos con *tiles*, de modo que los hilos de cada grupo puedan "flotar" entre los núcleos lógicos que comparten el mismo *tile*. Si bien un hilo luego de un *context switch* ahora tiene más oportunidades de reanudarse rápidamente (son el doble de núcleos lógicos en los que un hilo puede retomar el trabajo en comparación con la granularidad *core*), la desventaja es que si su ejecución se reanuda en el otro núcleo físico del mismo *tile*, su *working set\** habrá quedado en la caché L1D "equivocada", por lo que probablemente aumentará la tasa de fallos de caché hasta que se restablezca su *working set* en la L1D de su nuevo núcleo físico. En la figura 2.8 se muestra un ejemplo de afinidad *compact* con granularidad *tile*.

Fig 2.8: Ejemplo de distribución de hilos con granularidad "tile" y tipo de afinidad "compact"

El *working set* en su sentido más estricto es el conjunto de páginas de memoria más utilizadas de un proceso. En un sentido más laxo podemos hablar de *working set* como "espacio de memoria más utilizado", ya sea por un proceso (con todo su conjunto de hilos), o como es en este caso, por un hilo individualmente.

### 2.3.5. MCDRAM y DDR

#### **Recomendaciones generales**

Si bien el ancho de banda de la memoria MCDRAM es sustancialmente mayor que el de la DDR (ver tabla 2.1), la latencia de la MCDRAM es incluso algo más alta (es decir, peor) que la latencia de la DDR cuando no hay suficiente demanda de ancho de banda. Por lo que en algunas aplicaciones que tienen una localidad espacial y temporal deficientes, es probable que se obtenga el mismo (o incluso mayor) rendimiento si sus estructuras de datos son guardadas en la memoria DDR. En los casos en que no haya mejora de rendimiento al usar la MCDRAM, probablemente resulte más apropiado utilizar solamente la DDR, ya que ademas con ésta no hay que preocuparse de la limitación de los 16 GB de la MCDRAM.

En el caso en que se elija el modo *flat* o el modo *hybrid*, las estructuras de datos <u>accedidas</u> <u>frecuentemente</u> deberían ser alojadas en la memoria MCDRAM. Si dichas estructuras de datos superan la capacidad de la MCDRAM (16 GB en modo *flat*, y 12 u 8 GB en *hybrid*), entonces lo ideal sería colocar la parte más utilizada de ellas en la MCDRAM, y las menos utilizadas en la DDR. No obstante, el esfuerzo que requiere este tipo de implementación es alto, y puede no alcanzar para superar el rendimiento arrojado con el modo de memoria *cache*, motivo por el cual dicho modo de memoria es el más popular.

#### Modelos de uso de la memoria MCDRAM

| Opción                               | Resumen                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No hacer nada                        | Un programa en el cual su <i>working set</i> encaja perfectamente en la memoria L2 podría tener buen rendimiento con la DDR sola. Aplicaciones <i>cache-friendly</i> podrían seguir obteniendo ventajas con el modo de memoria <i>cache</i> . No obstante, para los programas que no pueden aprovechar bien la memoria caché, puede que obtengan algún beneficio de rendimiento si se selecciona el modo de memoria <i>flat</i> y se deja la MCDRAM sin utilizar. |

| Modo cache                           | Es trivial intentarlo. No implica ningún cambio en el código. En el KNL se puede dedicar el 100%, 50% o el 25% de la memoria MCDRAM como caché.                                                                                                                                                                                                                                                                                                                   |

| Las opciones res                     | tantes solo son útiles en los modos de memoria flat y hybrid                                                                                                                                                                                                                                                                                                                                                                                                      |

| numactl<br>(NUMA<br>Control utility) | <u>Sin cambios en el código</u> : Si está instalado el comando numactl, se lo puede utilizar para establecer previo a la ejecución de un programa, que todas las asignaciones de memoria se hagan en la MCDRAM (incluyendo <i>stacks</i> y segmentos de datos).                                                                                                                                                                                                   |

| autohbw                              | Sin cambios en el código: Se puede utilizar la librería autohbw (parte del proyecto memkind) para que efectúe las asignaciones de memoria, desde un rango de direcciones determinado, a la MCDRAM.                                                                                                                                                                                                                                                                |

| memkind                              | <u>Implica cambios en el código</u> : Utilizando la librería memkind, se puede tener control por software de dónde se asigna memoria en cada caso, si en la DDR o en la MCDRAM.                                                                                                                                                                                                                                                                                   |

Tabla 2.2: Modelos de uso de la memoria MCDRAM.

Fuente: Fig 3.2 [8, p. 29]

## 2.3.6. Procesamiento vectorial (SIMD)

#### Instrucciones SIMD en el Xeon Phi KNL

El Xeon Phi KNL es un procesador concebido desde cero con las unidades de procesamiento vectorial de 512 bits como pilares centrales de su poder de cómputo, relegando a un lugar más secundario a las unidades de ejecución de cómputo escalar. Por este motivo resulta esencial que una aplicación esté vectorizada en la mayor medida posible si se quiere sacar el máximo provecho al KNL.

Una aplicación diseñada y compilada para el KNL debería utilizar (siempre que sea posible) a los conjuntos de instrucciones AVX-512 (procesa más cantidad de datos en simultáneo), o en su defecto a los conjuntos AVX de 256 bits. Se debe evitar a toda costa el uso de instrucciones SSE y x87. Si bien esta arquitectura, con respecto a las anteriores, reduce en gran medida el impacto de mezclar instrucciones AVX con SSE, no obstante no logra anular del todo la pérdida de rendimiento. El uso de instrucciones SSE se deja solo como "aceptable" en caso de que estas provengan del uso de librerías *legacy*, las cuales no puedan ser reemplazadas por librerías equivalentes que hagan uso de los conjuntos AVX más modernos.

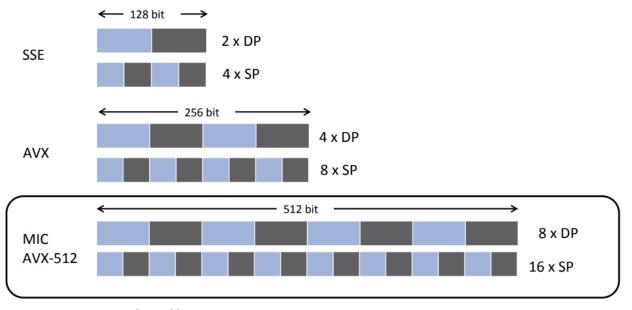

En la figura 2.9 se presenta de forma gráfica la diferencia entre los registros SIMD del KNL (SSE, AVX*x* y AVX-512) con los respectivos datos en punto flotante que caben en ellos.

Fig 2.9: Comparación gráfica del ancho de los registros SIMD del KNL, con la cantidad y tamaño de los datos que caben en ellos.

Fuente: [28, p. 6]

#### Vectorización de algoritmos

Para vectorizar algoritmos para el KNL se pueden utilizar las mismas técnicas disponibles para cualquier *multi-core*:

- 1. <u>Vectorización automática</u>: también llamada "autovectorización". Es la vectorización que realizan automáticamente los compiladores cuando están compilando en modos de optimización elevados. Se los puede ayudar mediante *flags* específicos que modifican las heurísticas del compilador, las cuales le permiten determinar en las distintas partes del código cuando sí amerita vectorizar y cuando no.

- 2. <u>Uso de librerías ya vectorizadas</u>: el uso de estas librerías brinda una forma fácil de lograr un código máquina vectorizado. No obstante, estas solo garantizan que la implementación de las funciones de las librerías estarán vectorizadas, pero no el código desde donde se las llama. Otro factor negativo, es que no siempre hay disponibles versiones vectorizadas de librerías, por lo que en muchos casos esto ni siquiera es una opción.

- 3. <u>Vectorización guiada (por directivas)</u>: Mediante el uso de directivas se puede indicar al compilador específicamente que debe vectorizar un *loop* determinado. A diferencia de la vectorización automática, la vectorización guiada evita que el compilador omita la vectorización del *loop* aún si sus heurísticas detectan falsas dependencias. La principal desventaja es que queda a cargo del programador asegurarse de que no haya dependencias de datos entre iteraciones del *loop*. Si el programador fuerza al compilador a vectorizar un *loop* que efectivamente tiene dependencias entre iteraciones esto haría que el compilador entregue como resultado un programa incorrecto.

- 4. <u>Vectorización manual</u>: Es el método más difícil y complejo de vectorizar algoritmos, pero a la vez es en el que el programador tiene el mayor control sobre <u>dónde</u> y <u>cómo</u> se vectoriza. En la vectorización manual se utilizan funciones intrínsecas que al compilarlas se mapean directamente con una o un grupo de instrucciones SIMD de código máquina. Como contrapartida, si se utiliza este método se pierde portabilidad, ya que habitualmente demanda fuertes modificaciones en el código para llevar la solución a otra plataforma.

En la tabla 2.3 se pueden apreciar de forma muy sintética las diferencias básicas entre las cuatro técnicas de vectorización.

|                                                      | V. Automática | V. con Librerías                     | V. Guiada     | V. Manual   |

|------------------------------------------------------|---------------|--------------------------------------|---------------|-------------|

| Implica modificar el código fuente                   | No            | Sí (muy poco)                        | Sí (muy poco) | Sí          |

| Facilidad de uso                                     | Muy fácil     | Fácil                                | Fácil         | Muy difícil |

| Permite controlar <u>dónde</u> se vectoriza          | Muy limitado  | Solo en llamados a func. de las lib. | Sí            | Sí          |

| Permite controlar <u>cómo</u> se implementa la vect. | No            | No                                   | No            | Sí          |

| *¹Libre de errores                                   | Sí            | Sí                                   | No            | No          |

| Es portable                                          | Sí            | Sí                                   | Sí            | No          |

Tabla 2.3: Tabla comparativa de técnicas de vectorización

#### 2.3.7. Alineamiento de datos en memoria

El alineamiento de datos en memoria no es una cuestión solo a tener en cuenta como una particularidad del procesador Xeon Phi KNL, más bien siempre fue un factor relevante desde el punto de vista del rendimiento, para todo el universo de procesadores. Si se desarrolla un programa en el cual se le da importancia a su tiempo de ejecución, el alineamiento de datos en memoria es una cuestión universal a tener en cuenta.

#### Almacenamiento alineado

Cuando los datos se almacenan en memoria principal, estos no siempre quedan ubicados de forma alineada con respecto al comienzo de cada linea de caché. Cuando esto ocurre, podrían quedar datos partidos entre dos lineas de caché diferentes, lo que implicaría dos accesos a memoria en lugar de uno solo ante una eventual lectura/escritura de un dato; y lo que es aún peor, un dato no alineado también podría quedar separado entre dos páginas de memoria distintas.

Los compiladores normalmente solucionan el problema de alineamiento por si solos, principalmente con las estructuras de datos estáticas, agregando el *padding* necesario entre los datos hasta lograr una alineación adecuada. No obstante, en el caso de arreglos en memoria dinámica, la solución de este problema no siempre está al alcance del compilador. Hay lenguajes de programación que brindan absoluta libertad al programador en el manejo de la memoria, al permitirle utilizar los arreglos en memoria dinámica como si se tratase de un arreglo de bytes, directamente mapeado a memoria. Esta libertad deja sin la posibilidad de que en tiempo de compilación se asegure una correcta alineación de los datos. Para estos casos, los lenguajes y compiladores proveen funciones alternativas de asignación de espacio en memoria dinámica, en

<sup>1</sup> Con "libre de errores" se hace referencia a que si bien el programador en el peor de los casos puede no lograr que el código quede vectorizado, sí se garantiza que si el código resultante efectivamente quedó vectorizado, entonces es correcto (sin errores lógicos). Desde ya que esto no contempla el caso en que el compilador o las librerías sean defectuosas, de todos modos dichos escenarios están fuera del alcance del programador.

las cuales se pasa por parámetro la cantidad de bytes con la que se quiere efectuar el alineamiento (deberá coincidir con el ancho de una linea de caché de la L1D). De esta forma, el primer elemento del arreglo quedará perfectamente alineado en la linea de caché. Luego queda a cargo del programador que los demás elementos del arreglo mantengan la alineación, pero ya la mayor parte del trabajo estará hecha; si el primer elemento está alineado, entonces el resto también lo estará si la longitud de cada uno de ellos es un divisor del ancho de la linea de caché.

#### Accesos alineados