## Análisis del Uso de un Cluster de Raspberry Pi para Cómputo de Altas Prestaciones

Pablo Sebastián Rodríguez Eguren Facultad de Informática Universidad Nacional de La Plata

Director: Esp. Franco Chichizola Director: Dr. Enzo Rucci

Tesina presentada para obtener el grado de  $Licenciado\ en\ Sistemas$  Mayo 2018

A mis padres Heber y Mabel, a mi hermano Mauro y a mi hermana Daiana, por el esfuerzo y acompañamiento que me brindaron a lo largo de la carrera;

a mi novia Vero por su cariño, comprensión y por incentivarme a seguir adelante;

a mis compañeros y directores, Franco y Enzo, por la paciencia, por dirigirme y hacer esta tesina posible;

al instituto III-LIDI por recibirme, rodearme de colegas de los cuales aprendo día a día, y por brindarme los medios y recursos para realizar esta tesina.

# Índice general

| 1. | $\mathbf{Intr}$                          | oducción                                                   |  |  |  |  |  |  |  |  |  |  |  |  |

|----|------------------------------------------|------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|

|    | 1.1.                                     | Motivación                                                 |  |  |  |  |  |  |  |  |  |  |  |  |

|    | 1.2.                                     | Objetivo y metodología                                     |  |  |  |  |  |  |  |  |  |  |  |  |

|    | 1.3.                                     | Desarrollos propuestos y resultados esperados              |  |  |  |  |  |  |  |  |  |  |  |  |

|    | 1.4.                                     | Organización de la tesina                                  |  |  |  |  |  |  |  |  |  |  |  |  |

| 2. | Pro                                      | cesamiento paralelo                                        |  |  |  |  |  |  |  |  |  |  |  |  |

|    | 2.1.                                     | ¿Qué es el procesamiento paralelo y para qué se utiliza?   |  |  |  |  |  |  |  |  |  |  |  |  |

|    | 2.2.                                     | Dificultades                                               |  |  |  |  |  |  |  |  |  |  |  |  |

|    | 2.3.                                     | Plataformas paralelas                                      |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.3.1. Plataformas de memoria compartida                   |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.3.2. Plataformas de memoria distribuida                  |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.3.3. Plataformas híbridas                                |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.3.4. Taxonomía de Flynn                                  |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.3.5. Multicores y clusters                               |  |  |  |  |  |  |  |  |  |  |  |  |

|    | 2.4. Modelos y librerías de programación |                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.4.1. Paradigma de pasajes de mensajes                    |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.4.2. Paradigma de memoria compartida                     |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.4.3. Paradigma híbrido                                   |  |  |  |  |  |  |  |  |  |  |  |  |

|    | 2.5.                                     | Diseño de algoritmos y técnicas para optimizar rendimiento |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.5.1. Etapa de descomposición                             |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.5.2. Etapa de mapeo                                      |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.5.3. Métodos para reducir overhead                       |  |  |  |  |  |  |  |  |  |  |  |  |

|    | 2.6.                                     | Modelo de algoritmos paralelos                             |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.6.1. Modelo SPMD                                         |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.6.2. Modelo Master-Slave                                 |  |  |  |  |  |  |  |  |  |  |  |  |

|    | 2.7.                                     | Métricas de rendimiento                                    |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.7.1. Tiempo de ejecución                                 |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.7.2. Speedup                                             |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.7.3. Eficiencia                                          |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.7.4. Escalabilidad                                       |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.7.5. MIPS y FLOPS                                        |  |  |  |  |  |  |  |  |  |  |  |  |

|    |                                          | 2.7.6. Rendimiento/Watt                                    |  |  |  |  |  |  |  |  |  |  |  |  |

|    | 2.8                                      | Resumen 9                                                  |  |  |  |  |  |  |  |  |  |  |  |  |

| 3. | Ras            | pberry          | Pi                                         |  |  |  |  |  |  |  |  |  |  |  |

|----|----------------|-----------------|--------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

|    | 3.1.           | Definic         | ciones                                     |  |  |  |  |  |  |  |  |  |  |  |

|    | 3.2.           |                 |                                            |  |  |  |  |  |  |  |  |  |  |  |

|    | 3.3.           | Áreas o         | de aplicación                              |  |  |  |  |  |  |  |  |  |  |  |

|    | 3.4.           |                 | as y modelos                               |  |  |  |  |  |  |  |  |  |  |  |

|    |                |                 | Familia Raspberry Pi                       |  |  |  |  |  |  |  |  |  |  |  |

|    |                |                 | Familia Raspberry Pi Zero                  |  |  |  |  |  |  |  |  |  |  |  |

|    |                |                 | Resumen comparativo                        |  |  |  |  |  |  |  |  |  |  |  |

|    | 3.5.           |                 | erry Pi 3                                  |  |  |  |  |  |  |  |  |  |  |  |

|    | 3.6.           |                 | as operativos y software disponible        |  |  |  |  |  |  |  |  |  |  |  |

|    | 3.7.           |                 |                                            |  |  |  |  |  |  |  |  |  |  |  |

|    | 3.8.           |                 | en                                         |  |  |  |  |  |  |  |  |  |  |  |

|    | <b>9.</b> 0.   | ICBUIII         |                                            |  |  |  |  |  |  |  |  |  |  |  |

| 4. | $\mathbf{Des}$ | pliegue         | e del cluster                              |  |  |  |  |  |  |  |  |  |  |  |

|    | 4.1.           | Descrip         | pción del hardware                         |  |  |  |  |  |  |  |  |  |  |  |

|    |                | 4.1.1.          | TV o Monitor VGA/HDMI                      |  |  |  |  |  |  |  |  |  |  |  |

|    |                | 4.1.2.          | Teclado USB                                |  |  |  |  |  |  |  |  |  |  |  |

|    |                | 4.1.3.          | Fuente de PC de 250W                       |  |  |  |  |  |  |  |  |  |  |  |

|    |                | 4.1.4.          | Switch 3COM Baseline 2226 Plus (3C16475BS) |  |  |  |  |  |  |  |  |  |  |  |

|    |                | 4.1.5.          | Cables Ethernet/RJ45                       |  |  |  |  |  |  |  |  |  |  |  |

|    |                | 4.1.6.          | Micro SD Verbatim de 16Gb                  |  |  |  |  |  |  |  |  |  |  |  |

|    |                | 4.1.7.          | Laptop o PC de escritorio                  |  |  |  |  |  |  |  |  |  |  |  |

|    |                | 4.1.8.          | Conexión a Internet                        |  |  |  |  |  |  |  |  |  |  |  |

|    | 4.2.           |                 | uración general                            |  |  |  |  |  |  |  |  |  |  |  |

|    | 7.2.           | _               | Instalación de Raspbian                    |  |  |  |  |  |  |  |  |  |  |  |

|    |                | 4.2.1. $4.2.2.$ | Encendido de la Raspberry Pi               |  |  |  |  |  |  |  |  |  |  |  |

|    |                | 4.2.3.          | Configuración inicial                      |  |  |  |  |  |  |  |  |  |  |  |

|    | 4.3.           |                 | uración del nodo master                    |  |  |  |  |  |  |  |  |  |  |  |

|    | 4.5.           |                 | Generación de claves                       |  |  |  |  |  |  |  |  |  |  |  |

|    |                | 4.3.1.          |                                            |  |  |  |  |  |  |  |  |  |  |  |

|    |                |                 | Configuración de red                       |  |  |  |  |  |  |  |  |  |  |  |

|    |                |                 | DHCP                                       |  |  |  |  |  |  |  |  |  |  |  |

|    |                | 4.3.4.          |                                            |  |  |  |  |  |  |  |  |  |  |  |

|    |                | 4.3.5.          | NAT                                        |  |  |  |  |  |  |  |  |  |  |  |

|    | 4.4            | 4.3.6.          | OpenMPI                                    |  |  |  |  |  |  |  |  |  |  |  |

|    | 4.4.           | 0               | uración del nodo worker                    |  |  |  |  |  |  |  |  |  |  |  |

|    |                | 4.4.1.          | Configuración de red                       |  |  |  |  |  |  |  |  |  |  |  |

|    | , _            |                 | NFS                                        |  |  |  |  |  |  |  |  |  |  |  |

|    | 4.5.           |                 |                                            |  |  |  |  |  |  |  |  |  |  |  |

|    | 4.6.           |                 | as del cluster                             |  |  |  |  |  |  |  |  |  |  |  |

|    | 4.7.           | Resum           | en                                         |  |  |  |  |  |  |  |  |  |  |  |

| ۳  | TD             | 1               |                                            |  |  |  |  |  |  |  |  |  |  |  |

| э. |                |                 | de rendimiento y eficiencia energética     |  |  |  |  |  |  |  |  |  |  |  |

|    | 5.1.           | _               | nentación de aplicaciones benchmark        |  |  |  |  |  |  |  |  |  |  |  |

|    |                | 5.1.1.          | Multiplicación de matrices                 |  |  |  |  |  |  |  |  |  |  |  |

|    |                | トロワ             | Incohi golyon                              |  |  |  |  |  |  |  |  |  |  |  |

|    |      | 5.1.3.  | N-r   | einas                        |                      |       |      |      |       |    |    |    |    |  |  |  |  |  |  | 93  |

|----|------|---------|-------|------------------------------|----------------------|-------|------|------|-------|----|----|----|----|--|--|--|--|--|--|-----|

|    | 5.2. | Prueba  | as re | aliza                        | $\operatorname{das}$ |       |      |      |       |    |    |    |    |  |  |  |  |  |  | 98  |

|    |      | 5.2.1.  | Pri   | mera                         | etar                 | oa de | e pr | ueba | as    |    |    |    |    |  |  |  |  |  |  | 100 |

|    |      | 5.2.2.  | Seg   | unda                         | etaj                 | pa d  | e pr | rueb | as    |    |    |    |    |  |  |  |  |  |  | 100 |

|    |      | 5.2.3.  | Ter   | cera                         | etap                 | a de  | prı  | ıeba | s.    |    |    |    |    |  |  |  |  |  |  | 100 |

|    | 5.3. | Resulta | ados  | $\operatorname{obt}\epsilon$ | enido                | s .   |      |      |       |    |    |    |    |  |  |  |  |  |  | 100 |

|    |      | 5.3.1.  | Pri   | mera                         | etar                 | oa de | e pr | ueba | as    |    |    |    |    |  |  |  |  |  |  | 100 |

|    |      | 5.3.2.  | Seg   | unda                         | etaj                 | pa d  | e pr | rueb | as    |    |    |    |    |  |  |  |  |  |  | 102 |

|    | 5.4. | Compa   | araci | ón co                        | on cl                | uste  | r de | mu   | ıltic | or | es | x8 | 36 |  |  |  |  |  |  | 112 |

|    |      | 5.4.1.  | Tie   | mpo                          | de e                 | jecu  | ción | ı .  |       |    |    |    |    |  |  |  |  |  |  | 112 |

|    |      | 5.4.2.  | Rei   | ndimi                        | .ento                | ٠     |      |      |       |    |    |    |    |  |  |  |  |  |  | 114 |

|    |      | 5.4.3.  | Efic  | cienci                       | a en                 | .ergé | tica |      |       |    |    |    |    |  |  |  |  |  |  | 117 |

|    | 5.5. | Trabaj  | os s  | imila                        | res .                |       |      |      |       |    |    |    |    |  |  |  |  |  |  | 119 |

|    | 5.6. | Resum   | en .  |                              |                      |       |      |      |       |    |    |    |    |  |  |  |  |  |  | 120 |

| 6. | Con  | clusion | 1es   | v tra                        | aba i                | os f  | utu  | ros  |       |    |    |    |    |  |  |  |  |  |  | 123 |

|    |      | Conclu  |       | •                            | •                    |       |      |      |       |    |    |    |    |  |  |  |  |  |  |     |

|    |      | Trabaj  |       |                              |                      |       |      |      |       |    |    |    |    |  |  |  |  |  |  |     |

# Índice de figuras

| 2.1.  | Plataforma de memoria compartida                                        | • |

|-------|-------------------------------------------------------------------------|---|

| 2.2.  | Plataforma de memoria distribuida                                       |   |

| 2.3.  | Plataforma de memoria híbrida                                           |   |

| 2.4.  | SISD                                                                    |   |

| 2.5.  | SIMD                                                                    |   |

| 2.6.  | MISD                                                                    |   |

| 2.7.  | MIMD                                                                    |   |

| 2.8.  | Modelo Fork-Join de OpenMP                                              | l |

| 3.1.  | Raspberry Pi Modelo A                                                   |   |

| 3.2.  | Raspberry Pi 2 Modelo B                                                 |   |

| 3.3.  | Raspberry Pi 3 Modelo B                                                 |   |

| 3.4.  | Raspberry Pi Zero                                                       |   |

| 3.5.  | Raspberry Pi Zero W                                                     |   |

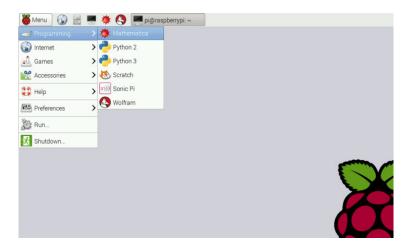

| 3.6.  | Entorno de escritorio PIXEL en Raspbian                                 |   |

| 3.7.  | Ubuntu Mate                                                             |   |

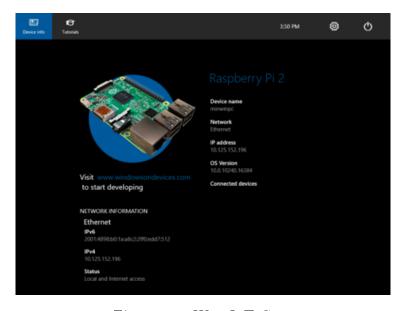

| 3.8.  | W10 IoT Core                                                            | 2 |

| 4.1.  | Cluster de RPi desplegado                                               |   |

| 4.2.  | Alimentación del cluster en detalle                                     |   |

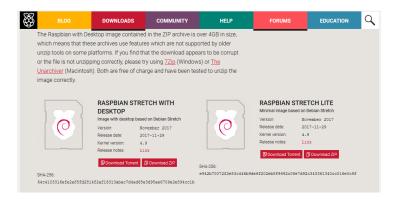

| 4.3.  | Versiones disponibles de Raspbian                                       |   |

| 4.4.  | Etcher y su simple e intuitiva interfaz                                 |   |

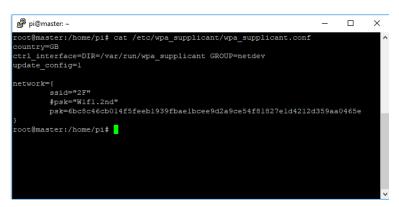

| 4.5.  | Contenido del archivo wpa_supplicant.conf                               |   |

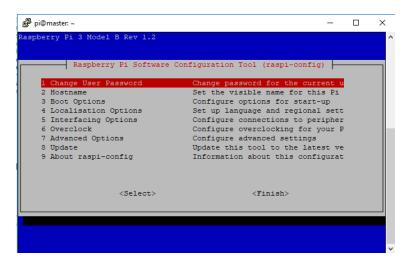

| 4.6.  | Menú del comando raspi-config                                           |   |

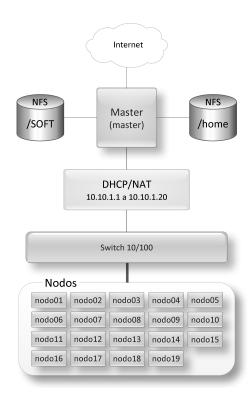

| 4.7.  | Arquitectura de red del cluster Raspberry Pi                            |   |

| 4.8.  | Salida del comando ompi_info                                            |   |

| 4.9.  | Pruebas de funcionamiento: Ping a $nodo 01$                             |   |

|       | Pruebas de funcionamiento: Conexión SSH a nodo01                        |   |

|       | Pruebas de funcionamiento: Copia de clave pública                       |   |

|       | Pruebas de funcionamiento: Directorios compartidos                      |   |

| 4.13. | Resultado de la ejecución de la aplicación: mpi_hola_mundo              | ) |

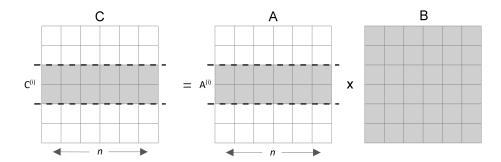

| 5.1.  | Cálculo de la submatriz                                                 | 7 |

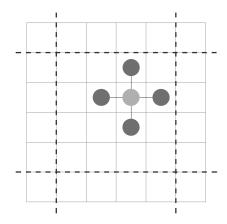

| 5.2.  | Jacobi solver: cálculo del nuevo valor                                  | ) |

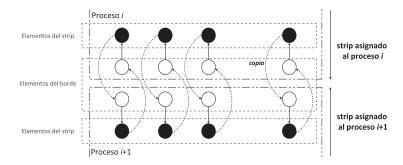

| 5.3.  | Representación de las estructuras de datos utilizadas en las pruebas de |   |

|       | Jacobi solver                                                           | ) |

| 5.4.  | Fase de distribución en la solución paralela de Jacobi-solver                         | 93  |

|-------|---------------------------------------------------------------------------------------|-----|

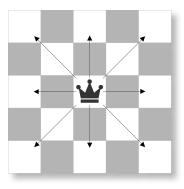

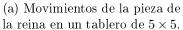

| 5.5.  | Problema de las N-reinas.                                                             | 95  |

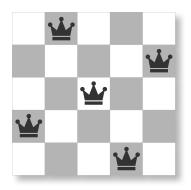

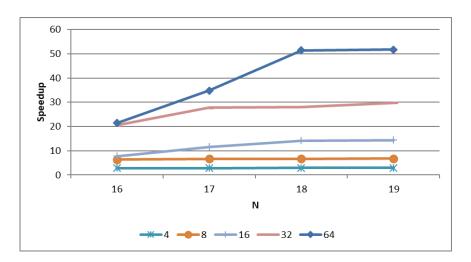

| 5.6.  | Speedups obtenidos por el algoritmo paralelo durante la fase de pruebas               | 103 |

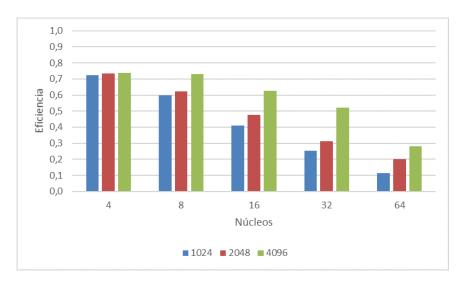

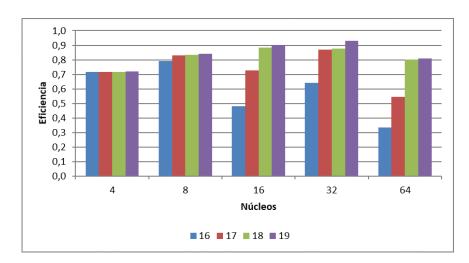

| 5.7.  | Eficiencias obtenidas con algoritmo paralelo para diferentes tamaños de problema      |     |

|       | y cantidad de núcleos.                                                                | 104 |

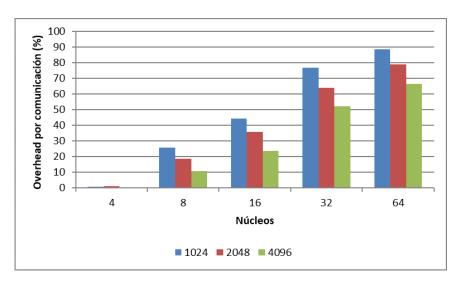

| 5.8.  | Porcentaje de overhead por comunicación obtenidos por los algoritmos paralelos        |     |

|       | para diferentes tamaños de problema y cantidad de núcleos.                            | 106 |

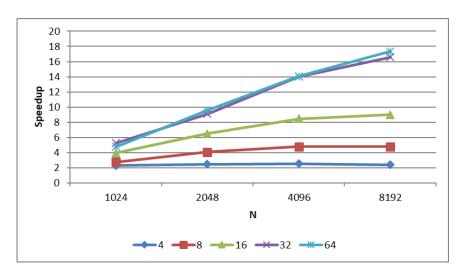

| 5.9.  | Speedups obtenidos en el algoritmo paralelo durante la fase de pruebas                | 108 |

| 5.10. | . Eficiencias obtenidas con el algoritmo paralelos para diferentes tamaños de proble- |     |

|       | ma y cantidad de núcleos.                                                             | 109 |

| 5.11. | . Speedups obtenidos por los algoritmos paralelos durante la fase de pruebas          | 111 |

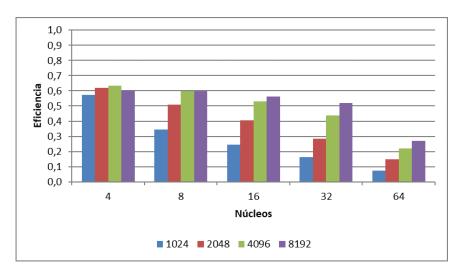

| 5.12. | . Eficiencias obtenidas por el algoritmos paralelos para diferentes tamaños de pro-   |     |

|       | blema y cantidad de núcleos.                                                          | 112 |

## Capítulo 1

## Introducción

Se presenta la motivación de esta tesina, y se detallan: el objetivo, la metodología, los desarrollos propuestos y los resultados esperados. Finalmente, se describe la organización de la tesina.

#### 1.1. Motivación

En la actualidad, los grandes sistemas de cómputo de altas prestaciones (HPC, por sus siglas en inglés) son dominados por procesadores de propósito general con dos conjuntos de instrucciones (x86 y Power) de tres empresas vendedoras (Intel, AMD e IBM) [1]. Estos procesadores han sido diseñados especialmente para ofrecer un alto rendimiento por núcleo, pero con costo económico (de cientos a miles de dólares) y demanda de potencia acordes (en el rango de 60-140W). En la búsqueda de construir sistemas más grandes que nos permita llegar a la escala de los Exaflops, resulta fundamental explorar otras estrategias que ofrezcan tasas de rendimiento costo-eficientes y que sean capaces de reducir el consumo energético de estos sistemas [2].

Durante décadas, el desarrollo de plataformas HPC estuvo focalizado casi únicamente en mejorar el rendimiento de las mismas. Esto provocó un crecimiento exponencial en los requerimientos de potencia de estos sistemas (no sólo para alimentarlos sino también para refrigerarlos), lo que a su vez repercutió en el costo económico de los mismos. Es por eso que, hoy en día, la reducción del consumo energético se ha vuelto unos de los principales desafíos para la comunidad HPC.

Entre las diferentes alternativas actualmente exploradas, se encuentra el uso de procesadores de bajo consumo como los ARM. Esta clase de procesadores ha sido especialmente diseñada para el mercado de dispositivos móviles y los sistemas em-

bebidos. Recientemente, los procesadores ARM han entrado al mercado de PCs y servidores y se espera que en el futuro incrementen significativamente su potencia de cómputo manteniendo el bajo consumo de potencia [3]. Para la comunidad HPC, este escenario presenta una oportunidad de emplear los procesadores ARM para construir sistemas de alto rendimiento.

En los últimos años, el uso de procesadores ARM se ha vuelto popular entre desarrolladores y entusiastas de la programación debido al surgimiento de computadoras de placa única (SBC, por sus siglas en inglés: Single Board Computer) como la Beagleboard [4], la Raspberry Pi [5] y la Pandaboard [6]. Esto ha llevado a la formación de varias comunidades de desarrollo que invierten tiempo y esfuerzo en portar una amplia gama de sistemas operativos, aplicaciones, librerías y herramientas a los sistemas ARM más populares [7].

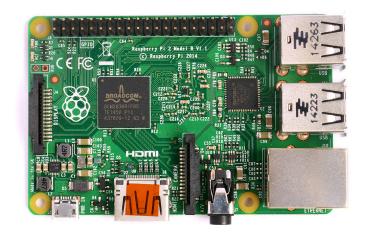

La Raspberry Pi (RPi) es una SBC de bajo costo desarrollada en el Reino Unido por la Fundación Raspberry Pi, con el objetivo de estimular la enseñanza de las ciencias de la computación en las escuelas. Desde su surgimiento, la RPi ha sido adoptada masivamente para una amplia gama de aplicaciones debido a su alto cociente rendimiento/precio, su tamaño reducido (similar al de una tarjeta de crédito) y su versatilidad [8]. En particular, desde el punto de vista del procesamiento paralelo, las RPi tienen múltiples núcleos, pueden conectarse en red y dan soporte a sistemas operativos y herramientas de programación tradicionales de HPC. Aunque sus núcleos no son potentes, el bajo consumo de potencia de las RPi las vuelven una opción atractiva desde el punto de vista energético. Es por eso que resulta interesante analizar la viabilidad del uso de un clúster de RPi para HPC.

## 1.2. Objetivo y metodología

El objetivo de esta tesina consiste en armar un cluster de placas RPi y analizar la viabilidad de su uso para cómputo de altas prestaciones. Para ello se realizarán las siguientes actividades:

- se estudiarán los fundamentos del procesamiento paralelo,

- se analizará la factibilidad del armado de un cluster de RPi contemplando las distintas opciones de configuración (tanto a nivel de hardware como de software),

- se seleccionarán aplicaciones que posean alta demanda computacional y diferentes características en su ejecución,

- se evaluará el rendimiento y la eficiencia energética del cluster armado para las aplicaciones seleccionadas comparándolo con un cluster de multicores convencional,

- se comparará la propuesta llevada a cabo y sus resultados con otros existentes en la literatura,

- se realizará un análisis de la viabilidad del uso de cluster de RPi para HPC.

## 1.3. Desarrollos propuestos y resultados esperados

Esta tesis propone el despliegue de un cluster de placas RPi que sea capaz de ejecutar aplicaciones paralelas empleando software de base y herramientas tradicionales de HPC. Entre los resultados esperados podemos mencionar:

- estudio del armado de un cluster de placas RPi. Este estudio contemplará las opciones de configuración tanto desde el punto de vista del hardware como del software y resultará útil para cualquier individuo que desee armar un cluster de esta clase.

- evaluación de rendimiento y eficiencia energética sobre un cluster de RPi y su comparación con un cluster de multicores x86. Mediante la ejecución de aplicaciones paralelas con diferentes características, este estudio permitirá caracterizar las tasas de prestaciones y eficiencia energética que un cluster de RPi puede alcanzar.

- análisis de la viabilidad de un cluster de RPi para HPC. Este análisis resultará valioso para cualquier individuo que deba decidir sobre el despliegue de un cluster de RPi para su institución, empresa u organización.

## 1.4. Organización de la tesina

El resto del documento se organiza de la siguiente forma:

• en el Capítulo 2 se estudian los fundamentos del procesamiento paralelo. En particular, se describen los principios de HPC, las arquitecturas paralelas y sus características, los modelos y herramientas para programación paralela junto a las técnicas usuales de optimización. Por último, se mencionan diferentes métricas de rendimiento reconocidas.

- en el Capítulo 3 se estudian las placas RPi, las cuales fueron seleccionadas para el armado del cluster desplegado en esta tesina. En primer lugar, se enuncia la historia del surgimiento de las primeras placas RPi, cómo logra insertarse en el mercado y el porqué de su auge. A continuación se describen las características y la evolución de cada modelo de placa RPi. Además, se mencionan los distintos sistemas operativos y sus principales características. Finalmente, se realiza una comparación teórica con procesadores x86.

- en el Capítulo 4 se presenta el despliegue y puesta a punto del cluster RPi. Primeramente, se menciona el hardware utilizado y la descripción en detalle del mismo (placas, switch, fuente de alimentación, etc). Después, se describe paso a paso la configuración común para los nodos y luego para cada uno de los nodos en concreto (master y worker). Por último, se describen las pruebas de integración y prueba del cluster para verificar el correcto funcionamiento del mismo.

- en el Capítulo 5 se analiza el rendimiento del cluster desplegado para esta tesina. Inicialmente, se describen las aplicaciones seleccionadas para la evaluación de prestaciones, detallando sus características relevantes. A continuación, se plasman y estudian los resultados obtenidos a fin de analizar el comportamiento del cluster RPi. Además, se realiza una comparación del cluster desplegado con un cluster de multicores x86, tanto desde el punto de vista del rendimiento computacional como de la eficiencia energética. Finalmente, se analizan trabajos relacionados disponibles en la literatura.

- en el Capítulo 6 se presentan las conclusiones de esta tesina y se describen algunas de las posibles líneas de trabajo futuro.

## Capítulo 2

## Procesamiento paralelo

# 2.1. ¿Qué es el procesamiento paralelo y para qué se utiliza?

Si nos transportamos un par de décadas atrás, una computadora tradicional contaba con una unidad de procesamiento individual para ejecutar las instrucciones especificadas en un programa. Los problemas eran divididos en series discretas de instrucciones, donde estas eran ejecutadas de a una por vez, unas tras otras. Una manera de incrementar el poder de cómputo es usar más de una unidad de procesamiento dentro de una única computadora o bien utilizar varias computadoras, trabajando todas juntos sobre el mismo problema. El problema es dividido en partes discretas, donde cada una de ellas es resuelta por una unidad de procesamiento individual de manera paralela. Se puede definir al procesamiento paralelo como el uso simultáneo de múltiples recursos computacionales para resolver un problema[9].

La necesidad de la computación paralela se origina por las limitaciones de los computadores secuenciales: integrando varios procesadores para llevar a cabo la computación es posible resolver problemas que requieren de más memoria o de mayor velocidad de cómputo. El objetivo principal de la computación paralela es reducir el tiempo de resolución de problemas computacionales, o bien para resolver problemas más grandes que no podrían ser resueltos por un computador convencional. Para llevar a cabo esto, es necesario emplear sistemas de cómputo de altas prestaciones y algoritmos paralelos que utilicen estos sistemas eficientemente.

Los problemas habituales en los cuales se aplica la programación paralela son: problemas con alta demanda de cómputo, problemas que requieren procesar una gran cantidad de datos, o problemas de tiempo real, en los que se necesita la respuesta en

un tiempo máximo. De esta forma, la comunidad científica usa la computación paralela para resolver problemas que sin el paralelismo serían intratables, o con tiempos de respuesta inaceptables. Algunos campos que se favorecen de la programación paralela son: predicciones y estudios meteorológicos, estudio del genoma humano, modelado de la biosfera, predicciones sísmicas, simulación de moléculas, modelización y simulación financiera, computación gráfica, realidad virtual, motores de búsqueda web, exploración de hidrocarburos, diseño de fármacos, entre otros.

Aunque tradicionalmente el objetivo primario de HPC fue reducir el tiempo de ejecución de las aplicaciones, en las últimas décadas la eficiencia energética ha cobrado un valor semejante. Esto se debe al elevado consumo energético y generación de calor de las arquitecturas paralelas que afectan al funcionamiento y repercuten en el costo, debido a la adquisición de equipos para refrigeración y al consumo energético que generan los mismos.

#### 2.2. Dificultades

Existen diversas dificultades que se pueden encontrar a la hora de escribir un programa paralelo. Por ejemplo, no siempre es posible paralelizar un programa; la paralelización requiere de tareas que no están presentes en la programación secuencial (descomposición del problema, comunicación y sincronización, mapeo, entre otras); mayor propensión a cometer errores por aumento de la complejidad; mayor dificultad a la hora de probar o depurar un programa; y por último, la fuerte dependencia entre el programa paralelo y la arquitectura de soporte para obtener alto rendimiento.

## 2.3. Plataformas paralelas

Una plataforma paralela consiste de dos o más unidades de procesamiento vinculadas a partir de algún tipo de red de interconexión. Es posible clasificarlas de dos formas, según su organización lógica o según su organización física. Se entiende como organización lógica, a la manera en que el programador visualiza la plataforma paralela. Por otro lado, la organización física se refiere al hardware real de la plataforma. A continuación se describen los diferentes tipos de plataformas paralelas.

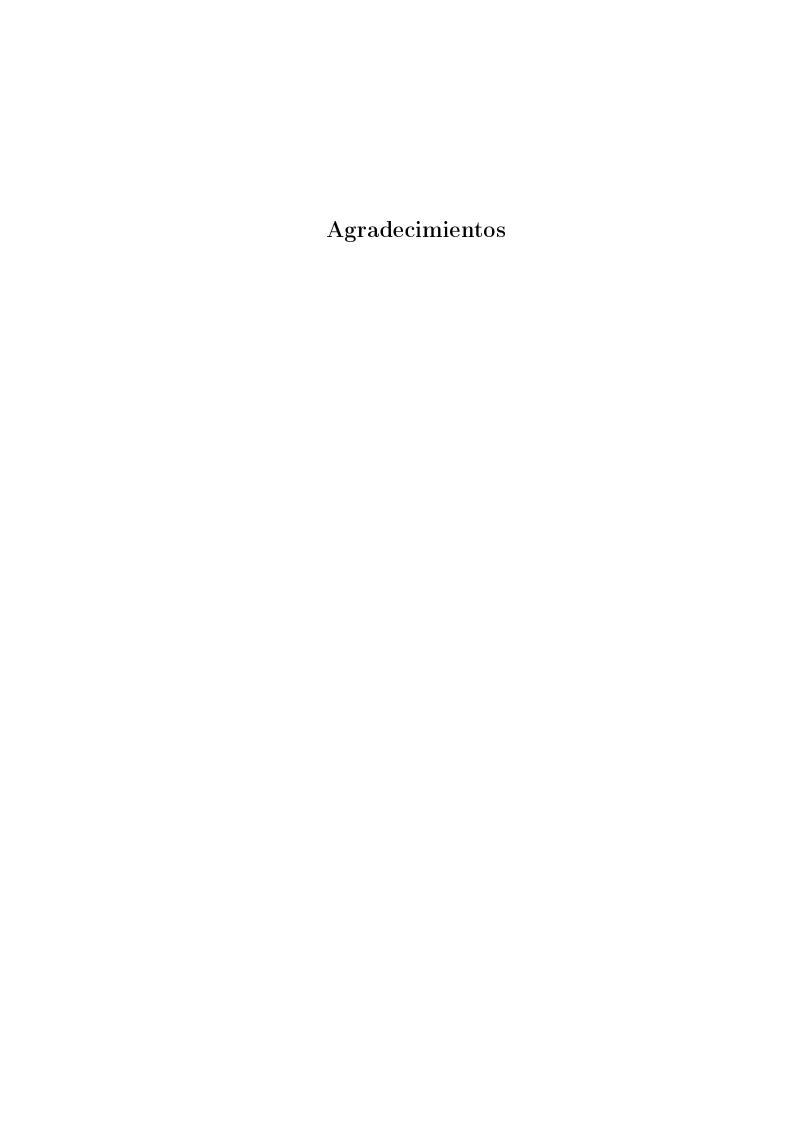

#### 2.3.1. Plataformas de memoria compartida

Un multiprocesador de memoria compartida consiste en dos o más unidades de procesamiento conectadas a múltiples módulos de memoria. La forma de conexión de estos elementos es a través de algún tipo de red de interconexión como puede ser un switch crossbar o un bus. En estos sistemas, existe un único espacio de direcciones, por lo que todas las unidades de procesamiento pueden acceder a la misma dirección de memoria, y modificar los datos almacenados en este espacio compartido. Si todas las unidades de procesamiento tienen el mismo tiempo para acceder a cualquier dirección de memoria, entonces se dice que el multiprocesador tiene acceso uniforme a memoria (UMA). Por el contrario, si el tiempo de acceso a algunas direcciones de memoria es mayor que a otras, entonces se dice que el multiprocesador es de acceso no uniforme a memoria (NUMA) [10, 11].

Idealmente, se desea que el sistema sea UMA. No obstante, los grandes sistemas de memoria compartida suelen ser de tipo NUMA dada la dificultad de implementar hardware que provea un acceso rápido a toda la memoria compartida. Por lo que cuentan con alguna estructura de memoria jerárquica o distribuida [9].

Tanto los sistemas UMA como los NUMA, cuentan con una memoria caché de alta velocidad para mantener los contenidos recientemente referenciados de las direcciones de memoria principal. A pesar de obtener mejoras con la presencia de cachés en las unidades de procesamiento, este tipo de memoria también acarrea la problemática de tener múltiples copias de una única palabra de memoria siendo manipulada por más de una unidad de procesamiento al mismo tiempo. Un ejemplo de este tipo de arquitecturas son los multicores.

Figura 2.1: Plataforma de memoria compartida.

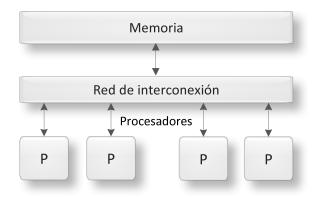

#### 2.3.2. Plataformas de memoria distribuida

Una plataforma de memoria distribuida consiste de varios nodos de procesamiento independientes con módulos de memoria locales, esto significa que cada uno cuenta con su propio espacio de direcciones. Además, estos nodos están conectados por una red de interconexión. Cada nodo puede ser una computadora individual o un multiprocesador de memoria compartida. Al contar con su propio espacio de memoria, el mismo no es accesible por el resto y los nodos deben comunicarse entre si enviándose mensajes. Éste intercambio de mensajes es utilizado para transferir datos, trabajo y sincronizar acciones entre nodos [11].

A la hora de escalar físicamente alguna de estas plataformas, resulta más fácil hacerlo en los sistemas de memoria distribuida que en los sistemas de memoria compartida [9].

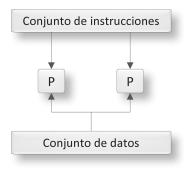

Figura 2.2: Plataforma de memoria distribuida.

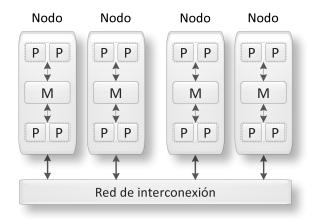

#### 2.3.3. Plataformas híbridas

Con la incorporación de los procesadores multicore a las arquitecturas de clusters tradicionales surgió una nueva plataforma híbrida conocida como cluster de multicores [12]. Con la aparición de esta plataforma, surgen nuevos tipos de comunicación debido a la heterogeneidad de la arquitectura [13], que se clasifican en: inter-nodo e intra-nodo. El primero se da entre los núcleos de distintos nodos y se lleva a cabo mediante envío de mensajes a través de la red de interconexión. El segundo se da entre los distintos núcleos que tiene un nodo y se lleva a cabo a través la jerarquía de memoria que estos núcleos comparten.

Figura 2.3: Plataforma de memoria híbrida.

## 2.3.4. Taxonomía de Flynn

Las computadoras paralelas se han utilizado durante muchos años, y se han propuesto y utilizado muchas alternativas arquitectónicas diferentes. En general, una computadora paralela se puede caracterizar como una colección de elementos de procesamiento que pueden comunicarse y cooperar para resolver rápidamente grandes problemas [14]. Esta definición es intencionalmente bastante vaga para capturar una gran variedad de plataformas paralelas. La definición no aborda muchos detalles importantes, incluidos el número y la complejidad de los elementos de procesamiento, la estructura de la red de interconexión entre los elementos de procesamiento, la coordinación entre los elementos de procesamiento, así como las características importantes del problema a resolver.

Para una investigación más detallada, es útil hacer una clasificación según las características importantes de una computadora paralela. Un modelo simple para tal clasificación está dado por la taxonomía de Flynn [15]. Esta taxonomía caracteriza las computadoras paralelas de acuerdo con el control global y los flujos de datos y control resultantes, dividiéndola en 4 categorías [16].

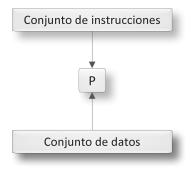

#### **SISD**

Una Secuencia de instrucciones y una secuencia de datos. Es un único procesador que interpreta una única secuencia de instrucciones para operar con los datos almacenados en una única memoria, no explota el paralelismo en las instrucciones ni en flujos de datos. Por lo tanto, SISD es la computadora secuencial convencional según el modelo de von Neumann [17].

Figura 2.4: SISD

#### **SIMD**

Una secuencia de instrucciones y múltiples secuencias de datos. Una sola instrucción controla paso a paso la ejecución simultanea y sincronizada de un cierto número de elementos de procesamiento. Cada uno de ellos tiene una memoria asociada, un computador que explota varios flujos de datos dentro de un único flujo de instrucciones para realizar operaciones que pueden ser paralelizadas de manera natural. Un ejemplo de estas arquitecturas son los procesadores vectoriales.

Figura 2.5: SIMD

#### **MISD**

Múltiples secuencias de instrucción y una secuencia de datos. Se transmite una secuencia de datos a un conjunto de procesadores, y cada uno de los cuales ejecuta una secuencia de instrucciones diferente. Poco común debido al hecho de que la efectividad de los múltiples flujos de instrucciones suele precisar de múltiples flujos de datos. Se han propuesto algunas arquitecturas teóricas, pero ninguna llegó a producirse en masa.

Figura 2.6: MISD

#### **MIMD**

Múltiples secuencias de instrucción y múltiples secuencias de datos. Consiste de un conjunto de procesadores que ejecutan simultáneamente secuencias de instrucción diferentes con conjuntos de datos diferentes. Los sistemas multiprocesador y los clusters son ejemplos de esta categoría.

Figura 2.7: MIMD

## 2.3.5. Multicores y clusters

#### Multicores

A principios de la década del 2000, el proceso tradicional de mejora de los procesadores llegó a su límite debido a la dicultad de extraer más paralelismo a nivel de instrucciones (ILP, por sus siglas en inglés) de los programas junto al excesivo consumo de potencia y generación de calor que alcanzaban los procesadores. Por tanto, se tuvieron que idear nuevas alternativas a la hora de diseñar procesadores que permitieran incrementar el rendimiento de los mismos. Así es como nacen los procesadores multicores, los cuales están formados por 2 o más núcleos de procesamiento en el mismo chip. Aunque estos núcleos son más limitados y lentos en comparación a sus

antecesores mononúcleo, su combinación mejora tanto el rendimiento global como la eficiencia energética del procesador.

Desde su surgimiento, grandes fabricantes de estas arquitecturas como Intel y AMD, han ido mejorando el diseño de los procesadores multicores a lo largo de las sucesivas familias de procesadores de propósito general lanzadas al mercado. Al principio contenían en una misma oblea dos procesadores mononúcleo. Más tarde, en las siguientes generaciones, han ido aumentando la cantidad de núcleos e incorporando cachés a varios niveles (L2 y L3), las cuales son compartidas por todos los núcleos o parte de ellos [18].

- Procesadores Intel: en la actualidad, Intel ofrece una amplia gama de procesadores, cada uno orientado a diferentes usos. A continuación se presentan la familia de procesadores Intel y sus características principales:

- Atom bajo consumo. Utilizados para dispositivos portátiles o aquellos donde el rendimiento energético es crítico.

- Celeron son los más económicos. Utilizados en computadoras de escritorio o portables. Poseen menos núcleos y memorias cache más pequeñas.

- Core mayor poder de cómputo, pensados para uso personal y profesional. Los primeros de la linea en integrar cache L3.

- o i3 los más modestos de la familia. La mayoría de sus modelos poseen la tecnología Hyper-Threading y memorias cache L3 hasta 8MB.

- i5 más potencia que los i3. La mayoría cuentan con 4 núcleos físicos, aunque los hay de 2 núcleos con Hyper-Threading. Cache L3 hasta 6MB y tecnología Turbo Boost.

- o i7 los más potentes. Los hay de 2, 4 y 6 núcleos, todos con tecnología Hyper-Threading y Turbo Boost. Caches L3 de hasta 20MB.

- Xeon los más potentes que fabrica Intel. Utilizados para workstation y servidores. Soporta múltiples sockets. Mayor número de núcleos (hasta 28 núcleos con Hyper-Threading). Memorias caché L3 más grandes (hasta 60MB). Soporte para detección y corrección de errores en la memoria RAM.

- Procesadores AMD: al igual que Intel, AMD ofrece una amplia gama de procesadores diseñados para diferentes propósitos. AMD ofrece 5 líneas principales de procesadores:

- Athlon ofrece un buen cociente precio-rendimiento y puede ser una buena opción para una computadora de uso personal. Se ofrecen en configuraciones, de 4 núcleos con memoria caché L2 de 4 Mb.

- **FX** son la gama media actual para el segmento de escritorio y sus modelos poseen 4 núcleos y memoria caché L3 de hasta 4Mb.

- Ryzen los actuales tope de gama de AMD. Cuentan con versiones que van desde los 4 núcleos y 4 hilos hasta los 8 núcleos y 16 hilos. Cache L3 hasta 32Mb.

- Opteron está destinada a los servidores y workstations, se los puede encontrar en versiones de 4, 6 y 8 núcleos. Estos potentes procesadores integran hasta 16 núcleos y 16Mb de memoria caché L3.

- **EPYC** linea nueva de procesadores para servidores y workstation. Superiores a los Opteron, se los puede encontrar en versiones de 8, 16, 24 y 32 núcleos con 16, 32, 48 y 64 hilos respectivamente. Poseen caché L3 hasta 64Mb.

A continuación se describen las características principales de cada familia AMD:

- Fusion corresponde a las APUs que integran CPU y GPU en el mismo chip.

- Bobcat está orientada al segmento de bajo consumo y de bajo costo.

- Bulldozer fue diseñada para computadoras de escritorio y servidores.

- Zen mejora el rendimiento por núcleo más que aumentar su número o la cantidad de hilos hardware.

- Procesadores ARM: Pertenecen a la familia de arquitecturas RISC (Reduced Instruction Set Computer) y son desarrollados por la empresa Advanced RISC Machines (ARM).

- ARM fabrica procesadores multicore RISC de 32 y 64 bits. Los procesadores RISC están diseñados para realizar una cantidad menor de tipos de instrucciones de computadora, de modo que puedan funcionar a mayor velocidad y realizar más instrucciones por segundo. Al eliminar las instrucciones innecesarias y optimizar las rutas, los procesadores RISC proporcionan un rendimiento sobresaliente a una fracción de la demanda de energía de los dispositivos

CISC¹ (Complex Instruction Set Computer). Los procesadores ARM se usan ampliamente en dispositivos electrónicos de consumo como teléfonos inteligentes, tabletas, reproductores multimedia y otros dispositivos móviles, como los weareables². Debido a su reducido conjunto de instrucciones, requieren menos transistores, lo que permite un tamaño de dado más pequeño para los circuitos integrados.

El diseño simplificado de los procesadores ARM permite un procesamiento multicore más eficiente y una codificación más sencilla para los desarrolladores. Si bien no tienen el mismo rendimiento de procesamiento que los productos de las marcas líderes, los procesadores ARM tienen un mejor rendimiento energético.

Existen diferentes familias ARM orientadas a distintos usos, los Cortex-R utilizados en procesadores de tiempo real; los Cortex-M, diseñados principalmente para dispositivos móviles por su bajo consumo; los SecurCore diseñado para dispositivos de seguridad; y finalmente la familia Cortex-A que es la utilizada en las SBC.

Aquellos procesadores basados en Cortex-A comparten una arquitectura y conjunto de características comúnmente admitidas. Los procesadores ARMv7-A admiten un conjunto de instrucciones de 32 bits y una ruta de datos, así como el conjunto de instrucciones Thumb2 de 16/32 bits. Los procesadores ARMv8-A Cortex-A añaden soporte para los estados de ejecución AArch32 / AArch64. Los procesadores Cortex-A de ARMv8.2-A agregan extensiones de arquitectura para un mayor impacto en el rendimiento del sistema. Todos los procesadores Cortex-A son compatibles con versiones anteriores y están respaldados por un fuerte ecosistema ARM.

Obviando las variantes que han quedado obsoletas, actualmente podemos encontrar las siguientes microarquitecturas:

• ARMv7-A estamos ante un modelo de 32 bits que ha servido para crear soluciones muy potentes. Con el salto a los 64 bits han quedado relegadas

<sup>&</sup>lt;sup>1</sup>Los microprocesadores CISC (Complex Instruction Set Computer, del español Computadora con conjunto de instrucciones complejas) tienen un conjunto de instrucciones que se caracteriza por ser muy amplio y permitir operaciones complejas entre operandos situados en la memoria o en los registros internos, en contraposición a la arquitectura RISC.

<sup>&</sup>lt;sup>2</sup>Wearable hace referencia al conjunto de aparatos y dispositivos electrónicos que se incorporan en alguna parte de nuestro cuerpo interactuando de forma continua con el usuario y con otros dispositivos con la finalidad de realizar alguna función concreta. Ejemplos de estos son: relojes inteligentes o smartwatchs, zapatillas de deportes con GPS, etc.

a un segundo plano y se mantienen sobre todo en productos donde lo que prima es el bajo consumo. Algunos de los procesadores que han basado en esta microarquitectura son: Cortex-A8 utilizado en los Apple iPod touch (tercera generación), y Cortex-A9, el cual puede ser encontrado en los celulares Galaxy Nexus.

- ARMv8-A primeras unidades de 64 bits de la arquitectura y la más utilizada actualmente, ya que integra soluciones versátiles que permiten crear sistemas en chip (SoCs, por sus siglas en inglés) equilibrados tanto en consumo como en rendimiento, sobre todo gracias a la combinación de diferentes variantes en configuraciones asimétricas (big.LITTLE). Tres de sus variantes más importantes son:

- Cortex-A53 son núcleos de bajo consumo que ofrecen un buen nivel de rendimiento, pero se encuentran por debajo de las otras dos variantes mencionadas a continuación. Se utilizan sobre todo en smartphones y tablets económicos y como segundo módulo de bajo consumo en CPUs con estructura big.LITTLE.

- Cortex-A57 son soluciones de alto rendimiento, aunque su consumo es mayor que el de los Cortex-A53. Actualmente se encuentran en productos de gama alta, aunque suelen ir combinados normalmente con los núcleos Cortex-A53 para mejorar la eficiencia conjunta del SoC en el que se integran.

- Cortex-A72 es una importante revisión que evoluciona desde los núcleos Cortex-A57. Mejoran el rendimiento, el consumo y permitiendo diseños más pequeños al ocupar una menor superficie dentro del encapsulado. No marcan una mejora sustancial en rendimiento, pero sí en consumo y reducción de costos.

- ARMv8.2-A es una evolución de la arquitectura ARMv8-A, la cual incluye cambios como un modelo de memoria mejorado, procesamiento de datos de punto flotante de precisión media e introduce el soporte RAS (Reliability, Availability and Serviceability). Ejemplos de procesadores de esta arquitectura son el Cortex-A55 y el Cortex-A75.

#### Clusters

Un cluster es un tipo de sistema de procesamiento paralelo compuesto por un conjunto de componentes de hardware estándares interconectadas vía algún tipo de

red, las cuales cooperan configurando un recurso que se ve como "único e integrado", más allá de la distribución física de sus componentes. Cada uno de los componentes que conforman un cluster se denomina nodo y son los encargados de llevar adelante el procesamiento. La construcción de los nodos de un clúster es relativamente fácil y económica debido a su flexibilidad: pueden tener todos la misma configuración de hardware y sistema operativo (clúster homogéneo), o tener diferente hardware y/o sistema operativo (clúster heterogéneo). Esta característica constituye un elemento importante en el análisis del rendimiento que se puede obtener de un clúster como máquina paralela.

Para que los nodos se comuniquen entre sí, es necesario proveerlos de un medio de interconexión mediante algún tipo de red de alta velocidad, por ejemplo, una red LAN. Sin embargo, no basta sólo con interconectar nodos para que un cluster funcione como tal, sino que es necesario proveer al mismo de un sistema de administración de cluster, el cual se encargue de interactuar con el usuario y las aplicaciones que se ejecuten en él.

Éste tipo de sistemas ofrece una manera rentable de mejorar el rendimiento (velocidad, disponibilidad, rendimiento, etc.) comparado con supercomputadoras de similares características [19]. A continuación se detallan los tipos de cluster según sus características.

- Cluster de alto rendimiento (High Performance Clusters): se caracterizan por ejecutar tareas que requieren de gran capacidad computacional, grandes cantidades de memoria, o ambos a la vez. El realizar estas tareas puede comprometer los recursos del cluster por periodos de tiempo indeterminados.

- Cluster de alta disponibilidad (High Availability): el objetivo principal de estos cluster se centra en la disponibilidad y la confiabilidad. Los clusters que pertenecen a estar categoría intentan brindar la máxima disponibilidad de los servicios que ofrecen. La confiabilidad es provista mediante software que detecta fallos y permite recuperarse frente a los mismos, mientras que por medio de hardware se previene tener un único punto de fallos.

- Cluster de alta eficiencia (High Throughout): son clusters cuyo objetivo de diseño se centra en ejecutar la mayor cantidad de tareas en el menor tiempo posible. Para poder llevar adelante esto debe existir independencia de datos entre las tareas individuales. El retardo entre los nodos del cluster no es considerado un gran problema.

Si bien cada tipo de cluster visto tiene sus características representativas, todos tienen un objetivo común: obtener un alto rendimiento a un bajo costo. Si a esto se le suma que pueden escalarse fácilmente, esto explica porqué el uso de clusters es hoy una de las posibilidades de cómputo paralelo/distribuido más elegidas.

## 2.4. Modelos y librerías de programación

Diversos lenguajes de programación y librerías han sido desarrollados para la programación paralela explícita. Estas difieren principalmente en la manera en que el usuario ve al espacio de direcciones. Los modelos se dividen básicamente en los que proveen un espacio de direcciones compartido o uno distribuido, aunque también existen modelos híbridos que combinan las características de ambos (este último modelo surge con la aparición de los procesadores multicore).

El espacio de direcciones influye significativamente sobre la manera en que los hilos o procesos intercambian la información. A continuación se describen cada uno de los modelos [11]

## 2.4.1. Paradigma de pasajes de mensajes

Cuando el espacio de direcciones es distribuido, cada proceso tiene su memoria local, y no existe una memoria compartida a la cual todos los procesos puedan acceder para intercambiar información. Es por ello que el intercambio de información entre procesos se da enviando y recibiendo mensajes.

#### Principios del paradigma de pasaje de mensajes

Como se mencionó anteriormente, en este paradigma varios procesos se ejecutan en paralelo y se comunican enviando y recibiendo mensajes. Los mismos operan sobre espacios de direcciones disjuntos, es decir, no tienen acceso a una memoria compartida. Toda la comunicación que pueda haber entre ellos se lleva adelante por intercambio de mensajes. Las operaciones básicas de comunicación son send y receive.

Existen diferentes protocolos para las operaciones send y receive: bloqueantes y no bloqueantes. Los protocolos bloqueantes no devuelven el control de la operación hasta que el dato a transmitir esté seguro. Si bien garantizan la corrección de las operaciones, pueden incurrir en overheads innecesarios por la ocurrencia de ocio, además de ser más propensos a ocasionar deadlocks. En sentido opuesto, los protocolos no bloqueantes devuelven el control inmediatamente luego de iniciar la operación send/recv, por lo

que el overhead asociado es mínimo. Sin embargo, la corrección de sus operaciones queda a cargo del programador.

#### MPI

La especificación MPI (Message Passing Interface) define un estándar para el pasaje de mensajes que puede ser utilizado desde los lenguajes C o Fortran, y potencialmente desde otros también. MPI define tanto la sintaxis como la semántica de un conjunto básico de rutinas, las cuales resultan útiles a la hora de escribir programas con mensajes. En la actualidad, existen diversas implementaciones para diferentes proveedores de hardware [20].

Todas las rutinas, tipos de datos y constantes en MPI tienen el prefijo "MPI\_". El código de retorno para operaciones terminadas exitosamente es MPI\_SUCCESS. Aunque MPI posee cientos de funciones, básicamente con 6 rutinas podemos escribir programas paralelos basados en pasaje de mensajes: MPI\_Init, MPI\_Finalize, MPI\_Comm\_size, MPI\_Comm\_rank, MPI\_Send y MPI\_Recv.

Para poder utilizar las rutinas provistas por MPI es necesario que todos los procesos invoquen la operación MPI\_Init. La misma inicializa el ambiente MPI. La rutina MPI\_Finalize debe ser llamada al finalizar la computación, ya que se encarga de realizar diferentes tareas de mantenimiento para poder cerrar el ambiente MPI.

También existen rutinas que proveen información del dominio de comunicación y de todos los procesos que están involucrados en la ejecución de una aplicación, las funciones que permiten adquirir esta información son:  $MPI\_Comm\_size$ , que indica la cantidad de procesos en el dominio de comunicación, y  $MPI\_Comm\_rank$  que indica el "rank" (identificador) del proceso dentro de un dominio de comunicación.

MPI también ofrece diferentes rutinas que implementan las operaciones básicas send y receive. Para comunicación bloqueante, ofrece una primitiva de recepción como:

- MPI\_Recv rutina básica para recibir datos de otro proceso. La operación se completa sólo después de que los datos hayan sido recibidos y copiados.

- MPI\_Send rutina básica para enviar datos a otro proceso. La operación se completa cuando el mensaje es recibido.

Al igual que para la comunicación bloqueante, por medio de las primitivas  $MPI\_Send$  y  $MPI\_Recv$ , MPI provee primitivas de recepción y emisión para comunicación no bloqueante. Las primitivas son  $MPI\_Irecv$  y  $MPI\_Isend$ . Además, para poder chequear la finalización de las operaciones send y receive no bloqueantes, MPI provee

dos funciones: MPI\_Test y MPI\_Wait. La primera chequea si una operación ha finalizado o no, y la segunda permite bloquear al proceso hasta que una operación no bloqueante realmente finalice.

MPI provee un conjunto de funciones que realizan operaciones de comunicación colectivas comúnmente usadas. Todas estas funciones toman como argumento un comunicador que define el grupo de procesos involucrados en la operación de comunicación. Todos los procesos pertenecientes a este comunicador participan en la operación y es necesario que todos ellos invoquen a la función correspondiente. Siempre que sea posible, conviene emplear estas operaciones para comunicaciones grupales dado que se encuentran optimizadas a nivel de librería. Entre las más usadas se encuentran:

- MPI Bcast Envía un mensaje a todos los procesos restantes.

- MPI Scatter Separa y distribuye datos entre todos los procesos.

- MPI\_Gather Recibe y concatena los datos enviados por todos los procesos restantes

- MPI Reduce Combina mensajes de todos los procesos.

### 2.4.2. Paradigma de memoria compartida

Cuando el espacio de direcciones es compartido, el proceso y sus hilos acceden al mismo espacio de memoria, y estos intercambian información leyendo y escribiendo sobre variables que son compartidas.

#### Hilos

En el modelo de hilos, cada proceso puede incluir múltiples flujos de control independientes los cuales son llamados hilos.

Un atributo característico es que los hilos de un proceso comparten el espacio de direccionamiento del mismo, es decir, tienen un espacio común. Cuando un hilo almacena un valor en el espacio de direcciones compartido, otro del mismo proceso también podrá accederlo [16].

A continuación se mencionan algunas ventajas del modelo de hilos:

Portabilidad del software: las aplicaciones multi-hiladas pueden ser desarrolladas en máquinas secuenciales y luego ser trasladadas a máquinas paralelas sin tener que realizar cambios.

- Ocultamiento de la latencia: una de las mayores fuentes de overhead, tanto en programas seriales como paralelos, es la latencia en el acceso a memoria, de la E/S y de la comunicación. La ejecución multi-hilada ayuda a ocultar la latencia, al poder intercalar la ejecución de los mismos.

- Planificación y balance de carga: usualmente resulta difícil obtener una distribución del trabajo balanceada en aplicaciones poco estructuradas y dinámicas. Los hilos permiten al programador especificar un gran número de tareas concurrentes que serán mapeadas a unidades de procesamiento de forma dinámica. De esta manera, se libera al programador de la responsabilidad de la planificación explícita y del balance de carga.

- Facilidad de programación y amplio uso: debido a las ventajas mencionadas anteriormente, los programas multi-hilados resultan más fáciles de escribir que los correspondientes programas utilizando pasaje de mensajes. Sin embargo, lograr igual rendimiento para ambos programas puede requerir un esfuerzo mayor.

#### Pthreads

POSIX Threads (Pthreads) es una API para la creación y manipulación de hilos, que ha emergido como estándar. Existen diversas implementaciones para los distintos sistemas operativos como por ejemplo: GNU/Linux, FreeBSD, NetBSD, OpenBSD, entre otras.

Para poder escribir un programa multihilado, es necesario contar con una función que permita crear hilos. Para ello la API Pthreads provee la función pthread create.

En muchas ocasiones un hilo debe esperar a que otro termine para poder realizar su trabajo. La función *pthread\_join* suspende la ejecución del hilo invocador hasta que el hilo especificado como parámetro finalice con su trabajo.

Cuando múltiples hilos intentan manipular el mismo dato, los resultados pueden ser incoherentes si no se toman los cuidados apropiados. Los programadores deben garantizar que las diferentes tareas concurrentes accedan a los datos en forma sincronizada de manera de obtener programas hilados que sean correctos. Pthreads provee soporte para implementar secciones críticas y operaciones atómicas usando mutex-locks. Asimismo, ofrece variables condition para los casos en que los hilos deben sincronizar por condición.

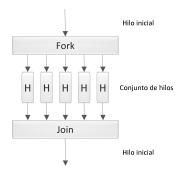

Figura 2.8: Modelo Fork-Join de OpenMP.

#### OpenMP

OpenMP es una API que reúne una colección de directivas, librerías y variables de entorno para la programación de aplicaciones paralelas sobre arquitecturas con memoria compartida, disponible para los lenguajes C, C++ y Fortran. Es una herramienta multiplataforma ya que posee versiones para diversas arquitecturas y sistemas operativos, haciendo que las aplicaciones paralelas que la utilizan sean fácilmente portables.

En general, el programa paralelo surge a partir de añadir simplemente directivas al programa secuencial que permiten: crear un conjunto de hilos, repartir tareas paralelas independientes entre ellos y sincronizarlos para el acceso de datos compartidos.

OpenMP utiliza el modelo fork-join (Figura 2.8), en el cual el programa comienza ejecutándose como un único hilo (llamado maestro). Cuando se encuentra la primera directiva paralela se crea un conjunto de hilos (cada uno ejecutará el mismo código), los cuales podrán repartirse el trabajo y/o coordinarse para el uso de datos compartidos a través del uso de directivas para tal fin. Al terminar la región paralela continúa la ejecución el hilo maestro.

Los hilos se ejecutarán dentro del mismo espacio de direcciones y podrán compartir el acceso a variables declaradas en el mismo; también se permite que una variable sea designada como privada a un hilo, en este caso cada hilo tendrá una copia que usará mientras dure la región paralela.

## 2.4.3. Paradigma híbrido

Los paradigmas de programación tradicionales (pasaje de mensajes y memoria compartida) no se adaptan naturalmente a los clusters de multicores. Al mismo tiempo, se espera que un modelo híbrido (combinación de pasaje de mensajes con memoria compartida) explote mejor sus características.

La idea básica es que las tareas que se encuentran en el mismo nodo se comuniquen y sincronicen por memoria compartida mientras que las que se encuentran en diferentes nodos lo hagan por pasaje de mensajes.

En la práctica, se usa generalmente MPI en combinación con OpenMP o Pthreads.

# 2.5. Diseño de algoritmos y técnicas para optimizar rendimiento

El diseño de aplicaciones paralelas básicamente se resume a dos etapas: descomposición y mapeo.

#### 2.5.1. Etapa de descomposición

Uno de los pasos fundamentales en el desarrollo de algoritmos paralelos es la división del trabajo en un conjunto de tareas que puedan ejecutarse en forma concurrente. No existe una única técnica que permita descomponer un problema. La elección de la misma está supeditada a las características propias del problema y a la elección del diseñador del algoritmo. Se debe tener en cuenta que una descomposición dada no siempre permite alcanzar el mejor algoritmo paralelo para un problema determinado. Esta descomposición puede realizarse de muchos modos. Un primer concepto es pensar en tareas de igual código (normalmente paralelismo de datos o dominio) pero también podemos tener diferente código (paralelismo funcional o tareas o de control).

#### Descomposición de datos

La descomposición de datos es un método potente y comúnmente utilizado para derivar concurrencia en aquellos algoritmos que trabajan sobre grandes estructuras de datos. En esta técnica, la descomposición se realiza en dos pasos. En el primer paso, se particionan los datos sobre los cuales se opera, mientras que en el segundo paso, se utiliza el particionamiento anterior para inducir una partición del trabajo a realizar en tareas. Por lo general, las tareas realizan el mismo trabajo o trabajos similares sobre las diferentes particiones de datos.

#### Descomposición funcional

El paralelismo funcional se refiere a la ejecución simultánea de distintos flujos de instrucciones. Estas instrucciones pueden ser aplicadas al mismo o distintos flujos de

datos (típicamente se da el segundo caso). Se realiza una descomposición funcional y las tareas generadas ejecutan independientemente, comunicándose cuando lo necesitan [11].

### 2.5.2. Etapa de mapeo

El siguiente paso luego de que el problema ha sido descompuesto en tareas, consiste en asociar dichas tareas a las unidades de procesamiento donde serán ejecutadas. A esta asociación se la conoce como mapeo y tiene como objetivo minimizar los overheads ligados a la ejecución paralela de las tareas. Las técnicas de distribución utilizadas en los algoritmos paralelos pueden clasificarse en dos categorías: estático y dinámico. Entre los factores que determinan que técnica emplear se encuentran el paradigma de programación elegido, el tipo de arquitectura, las características de las tareas y la interacción que se da entre estas [11].

#### Mapeo estático

En las técnicas de mapeo estático, las tareas se distribuyen entre los procesadores antes de comenzar con la ejecución del algoritmo concreto. En general es más fácil de diseñar e implementar, y es más eficiente (si se logra balancear la carga de trabajo); pero requiere que se tenga conocimiento a priori de la cantidad y tamaño de las tareas a realizar.

#### Mapeo dinámico

El mapeo dinámico es necesario cuando el estático puede llevar a una distribución de carga de trabajo con un alto grado de desbalance entre los procesadores, o cuando las tareas a realizar se generan dinámicamente durante la ejecución de la aplicación. En las técnicas de mapeo dinámico, el trabajo (datos o tareas) se distribuye entre los procesadores durante la ejecución del algoritmo. Esta clase de mapeo es la mejor opción cuando la cantidad o tamaño de las tareas no son conocidos a priori [11].

## 2.5.3. Métodos para reducir overhead

El overhead generado por la interacción entre procesos limita la eficiencia que un programa paralelo puede alcanzar. Son varios los factores que inciden sobre el overhead generado por la interacción: el volumen de datos intercambiados, la frecuencia de la interacción, etc.

Entre los métodos para reducir overhead, se encuentran: maximización de la localidad de datos para combatir las limitaciones del sistema de memoria, minimización de la competencia de recursos para evitar interacciones innecesarias, solapamiento de cómputo con comunicaciones para reducir tiempos ociosos, replicación de datos o cómputo para evitar comunicaciones, uso de operaciones de comunicación colectivas, entre otros.

## 2.6. Modelo de algoritmos paralelos

Un modelo de algoritmo permite estructurar la computación de un algoritmo paralelo. Es la combinación de las técnicas de descomposición y mapeo elegidas junto a una estrategia para reducir overhead. Según [11], existen diferentes modelos de algoritmos paralelos, como el SPMD (Single Program Multiple Data), grafo de tareas, productor-consumidor o pipeline, master/slave, entre otros. Se describen a continuación los usados en esta tesina.

#### 2.6.1. Modelo SPMD

En el modelo SPMD (Single Program Multiple Data) se genera un programa único que cada nodo ejecuta sobre una porción diferente del dominio de datos. Por medio de instrucciones en el código se puede hacer que cada nodo tome distintos caminos del programa.

La implementación de un programa que siga este modelo involucra dos grandes fases: elección de la distribución de datos y generación del programa paralelo [21]. En la etapa de elección de la distribución de datos se determina que nodo procesa cada dato. Una mala distribución de los datos podría repercutir directamente sobre la carga de trabajo y sobre la cantidad de comunicaciones generadas.

#### 2.6.2. Modelo Master-Slave

En el modelo Master/Slave (o también conocido como Master/Worker), un proceso actúa como administrador (master) coordinando a todos los demás procesos que funcionan como esclavos (workers). El master es el encargado de descomponer el problema en tareas pequeñas, distribuirlas entre los diferentes procesos worker, y recibir los resultados parciales para componer la solución final del problema. Los workers realizan un procesamiento muy simple: reciben una tarea a realizar, la procesan, y

envían los resultados al master. En ocasiones, el master también computa en simultáneo con los workers. Este ciclo puede repetirse hasta que el master no tenga más tareas para resolver [11].

## 2.7. Métricas de rendimiento

Es importante estudiar el rendimiento de programas paralelos con el fin de determinar el mejor algoritmo, evaluar plataformas de hardware, y examinar los beneficios del paralelismo. Para ello se introduce una serie de métricas que permitirán realizar el análisis deseado.

#### 2.7.1. Tiempo de ejecución

El tiempo de ejecución secuencial corresponde al tiempo de ejecución de un programa secuencial que por lo tanto emplea una única unidad de procesamiento. El tiempo de ejecución paralelo es el tiempo que transcurre desde el momento en que el procesamiento paralelo comienza hasta que el último proceso finaliza su ejecución. Se expresa el tiempo de ejecución secuencial como  $T_s$  y el tiempo de ejecución paralelo como  $T_p$  [11].

## 2.7.2. Speedup

El speedup refleja el beneficio relativo de paralelizar la solución a un problema. Se define como el cociente entre el tiempo requerido por la solución secuencial utilizando la unidad de procesamiento más potente de la arquitectura paralela y el tiempo requerido por la solución paralela de interés utilizando p unidades de procesamiento. A continuación se ilustra la ecuación que permite calcular esta métrica.

$$S = \frac{T_s}{T_p} \tag{2.1}$$

Específicamente, el speedup indica cuántas veces más rápido se obtiene la solución al problema utilizando la solución paralela con p unidades de procesamiento con respecto a la solución secuencial.

Cuando hacemos referencia a la solución secuencial se debe tener en cuenta que puede existir más de un algoritmo que resuelva el problema. Se debe elegir el que soluciona el problema en la menor cantidad de tiempo. De otra manera no es justa la comparación con el algoritmo paralelo [11].

De acuerdo al resultado obtenido de la Ecuación 2.1 se pueden obtener tres tipos de speedup:

Speedup lineal también llamado speedup perfecto debido a que el algoritmo paralelo se ejecuta p veces más rápido que el algoritmo secuencial.

Speedup sublineal es el caso más frecuente en el cual el speedup obtenido es menor que p debido a factores como comunicación, sincronización, etc.

Speedup superlineal es el caso menos frecuente, en el cual el speedup obtenido supera a p. Esta situación puede darse por 2 motivos. El primero es porque el algoritmo paralelo realiza menos trabajo que la versión secuencial, como es el caso de los recorridos en árboles o grafos. El segundo es por una mejora en la localidad de datos al distribuir los mismos, dejando a la versión secuencial en desventaja [9].

#### 2.7.3. Eficiencia

La eficiencia es una medida que refleja cuan bien utilizadas son las unidades de procesamiento para resolver el problema. En arquitecturas homogéneas la eficiencia (E) se define como el cociente entre el speedup (S) y la cantidad de elementos de procesamiento usados (p), como se indica en la ecuación 2.2.

$$E = \frac{S}{p} \tag{2.2}$$

Se puede obtener una eficiencia igual a 1 si el speedup obtenido con p unidades de procesamiento es igual a p. Generalmente, debido a los costos que implican la sincronización y la comunicación, el speedup es menor a p, lo que lleva a la eficiencia a ser menor a 1.

#### 2.7.4. Escalabilidad

En muchos casos las aplicaciones paralelas son diseñadas y probadas para pequeños problemas y/o en un número reducido de elementos de procesamiento, a pesar de que se deban utilizar en problemas y arquitecturas mucho mayores. Mientras que el desarrollo y prueba de la solución paralela se simplifica al utilizar instancias reducidas del problema y de la arquitectura, el rendimiento es muy difícil de predecir en forma precisa basado en esos resultados. Esto se debe a que los algoritmos pueden tener

distinto comportamiento (referido al rendimiento) para los diferentes tamaños de problema y dimensiones de la arquitectura utilizada.

La escalabilidad de un sistema paralelo es una medida de la capacidad de incrementar el speedup en proporción a la cantidad de procesadores de la arquitectura, reflejando la habilidad de utilizar efectivamente el incremento de los recursos de procesamiento. Su análisis es necesario para elegir la mejor combinación de algoritmo y arquitectura para resolver un problema bajo distintas restricciones sobre el crecimiento del tamaño del problema o de los recursos de procesamiento

#### 2.7.5. MIPS y FLOPS

Una medida de rendimiento que a veces se usa en la práctica para evaluar un sistema informático es la tasa de millones de instrucciones por segundo (MIPS). La tasa de MIPS de A esta definida como:

$$MIPS(A) = \frac{Instrucciones(A)}{T(A) \times 10^6}$$

donde instrucciones (A) es el número de instrucciones ejecutadas por el programa A y T(A) es el tiempo de ejecución de dicho programa.

Usar las tasas de MIPS como medida de rendimiento tiene algunos inconvenientes. Primero, la tasa de MIPS solo considera el número de instrucciones, lo que favorece a los procesadores con instrucciones simples sobre los procesadores con instrucciones más complejas. En segundo lugar, la tasa MIPS de un programa no se corresponde necesariamente con su tiempo de ejecución: al comparar dos programas A y B en un procesador X, B puede tener una tasa de MIPS más alta que A, pero A tiene un tiempo de ejecución más pequeño [16].

Para programas con cálculos científicos, a veces se utiliza la velocidad MFLOPS (Millones de operaciones de coma flotante por segundo). La tasa de MFLOPS de un programa A está definida por

$$MFLOPS(A) = \frac{\text{instrucciones \_pf}(A)}{T(A) \times 10^6}$$

,

donde instrucciones pf(A) es el número de operaciones de coma flotante ejecutadas por A. La tasa MFLOPS no se basa en el número de instrucciones ejecutadas, como es el caso de la tasa MIPS, sino en el número de operaciones aritméticas en

valores de coma flotante realizado por la ejecución de sus instrucciones. Las instrucciones que no realizan operaciones de punto flotante no tienen efecto en la velocidad MFLOPS. Dado que se usa la cantidad efectiva de operaciones realizadas, la tasa de MFLOPS proporciona una comparación justa de las diferentes versiones de programa que realizan las mismas operaciones, y las mayores tasas de MFLOPS corresponden a tiempos de ejecución más rápidos.

Una desventaja de utilizar la tasa MFLOPS como medida de rendimiento es que no hay diferenciación entre los diferentes tipos de operaciones de coma flotante realizadas. Por lo tanto, los programas con operaciones de coma flotante más simples son preferibles a los programas con operaciones más complejas. Sin embargo, la tasa MFLOPS es adecuada para comparar versiones de programa que realizan las mismas operaciones de coma flotante [16].

## 2.7.6. Rendimiento/Watt

El consumo energético se ha vuelto uno de los mayores desafíos en el campo de la computación. Es por eso que se necesita contar con métricas con las cuales sea posible medir o estimar la eficiencia energética. Una medida aceptada es el número de FLOPS por Watt requerido (FLOPS/W) [22].

## 2.8. Resumen

La computación paralela se origina por las limitaciones de los computadores secuenciales: integrando varios procesadores para llevar a cabo la computación es posible resolver problemas que requieren de más memoria o de mayor velocidad de cómputo. Su objetivo principal es reducir el tiempo de resolución de problemas computacionales, o bien para resolver problemas grandes que no podrían ser resueltos por un computador convencional. Los problemas habituales en los cuales se aplica la programación paralela son: problemas con alta demanda de cómputo, problemas que requieren procesar una gran cantidad de datos, o problemas de tiempo real, en los que se necesita la respuesta en un tiempo máximo. Sin embargo, en las últimas décadas la eficiencia energética ha cobrado un valor semejante. Esto se debe al elevado consumo energético y generación de calor de las arquitecturas paralelas que afectan al funcionamiento y repercuten en el costo, debido a la adquisición de equipos para refrigeración y al consumo energético que generan los mismos.

Ahora bien, desarrollar soluciones paralelas no es tarea sencilla, a lo que pueden

presentarse dificultades. Existen diversas dicultades que se pueden encontrar a la hora de escribir un programa paralelo. Por ejemplo, no siempre es posible paralelizar un programa; la paralelización requiere de tareas que no están presentes en la programación secuencial (descomposición del problema, comunicación y sincronización, mapeo, entre otras); mayor propensión a cometer errores por aumento de la complejidad; mayor dificultad a la hora de probar o depurar un programa; y por último, la fuerte dependencia entre el programa paralelo y la arquitectura de soporte para obtener alto rendimiento.

Por otro lado, también es importante conocer la plataforma donde se aplicará la solución. Así como se pueden clasificar las dificultades en físicas y lógicas, también se lo puede hacer con las plataformas paralelas. Se entiende como organización lógica, a la manera en que el programador visualiza la plataforma paralela, por otro lado, la organización física se refiere al hardware real de la plataforma; se pueden identificar: plataforma de memoria compartida (dos o más unidades de procesamiento conectadas a múltiples módulos de memoria, interconectados entre si por una red) y plataformas de memoria distribuida (p nodos de procesamiento independientes con módulos de memoria locales). En la actualidad, con la incorporación de los procesadores multicore a las arquitecturas de clusters tradicionales se puede identificar un tercer tipo: las plataformas híbridas.

A principios de la década del 2000, el proceso tradicional de mejora de los procesadores llegó a su límite debido a la dicultad de extraer más paralelismo a nivel de instrucciones (ILP, por sus siglas en inglés) de los programas junto al excesivo consumo de potencia y generación de calor que alcanzaban los procesadores. Por tanto, se tuvieron que idear nuevas alternativas a la hora de diseñar procesadores que permitieran incrementar el rendimiento de los mismos. Así es como nacen los procesadores multicores, los cuales están formados por 2 o más núcleos de procesamiento en el mismo chip. Auquue estos núcleos son más limitados y lentos en comparación a sus antecesores mononúcleo, su combinación mejora tanto el rendimiento global como la eficiencia energética del procesador.

En la actualidad es posible encontrar grandes fabricantes de estas arquitecturas, tales como Intel, AMD, y ARM. Cada uno ofreciendo una amplia variedad de familias.

Un cluster es un tipo de sistema de procesamiento paralelo compuesto por un conjunto de componentes de hardware estándares interconectadas vía algún tipo de red, las cuales cooperan configurando un recurso que se ve como "único e integrado", más allá de la distribución física de sus componentes. Según sus características un cluster puede ser catalogado como: cluster de alto rendimiento (High Performance Clusters),

cluster de alta disponibilidad (High Availability) o cluster de alta eficiencia (High Throughout). Si bien cada tipo de cluster tiene sus características representativas todos tienen un objetivo común, obtener un alto rendimiento a un bajo costo. Si a esto se le suma que pueden escalarse fácilmente, esto explica porqué el uso de clusters es hoy una de las posibilidades de cómputo paralelo/distribuido más elegidas.

A la hora de programar es importante conocer sobre que espacio de direcciones se está trabajando. Los modelos se dividen básicamente en los que proveen un espacio de direcciones compartido o uno distribuido, aunque también existen modelos híbridos que combinan las características de ambos (este último modelo surge con la aparición de los procesadores multicore).